Xilinx DDR3 MIG IP实战:创建与配置详解

需积分: 0 96 浏览量

更新于2024-06-30

1

收藏 1.7MB PDF 举报

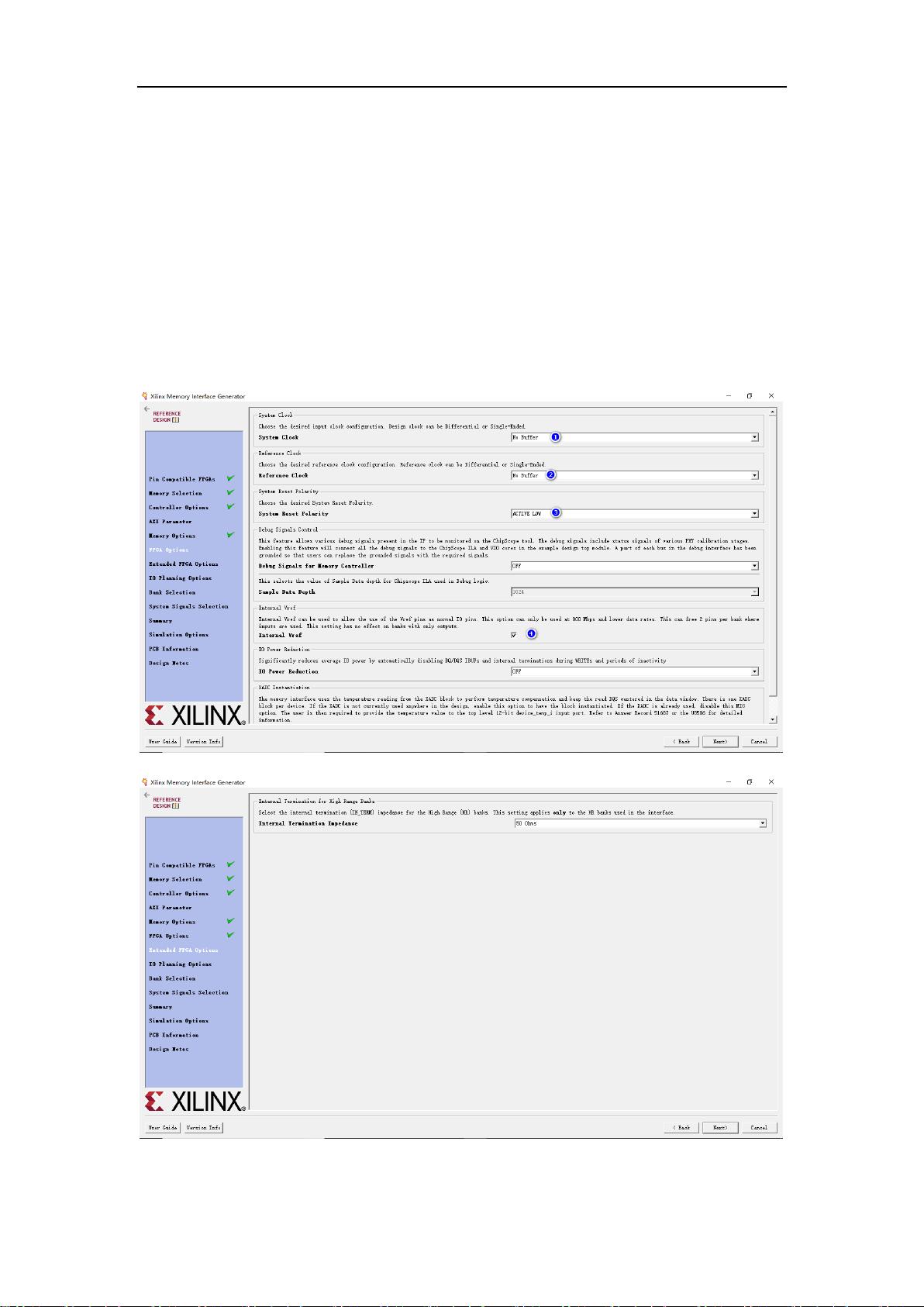

本文主要介绍了Xilinx FPGA中利用Memory Interface Generator (MIG) IP进行DDR3控制的深入应用,特别是针对第二篇内容,即如何在Digilent Arty Artix-35TFPGA开发板上创建和配置DDR3 SDRAM MIG IP。以下是详细步骤和关键知识点:

1. DDR3基础知识:首先,文章提及了所使用的MT41K128M16JT-125 DDR3模块的基本信息,包括其工作频率(333.33 MHz)和内存特性。

2. MIG IP创建过程:在Vivado 2018.1环境中,用户从IP Catalog搜索并选择MemoryInterfaceGenerator(MIG7Series)。创建过程中,组件名称被设置为“ddr3_ip”,并且在兼容性选择上不做限制,直接进入下一步。

- **ClockPeriod**:这是决定控制器工作频率的关键参数,受到FPGA和器件速度等级的影响。在这里选择了3000ps(333.33MHz),表明系统支持的最高数据传输速率。

- **PHY to Controller Clock Ratio**:这个比例决定物理层时钟与控制器时钟之间的关系。2:1比率虽然降低了最大存储器接口频率,但延迟较低;而4:1比率提供了更高的数据速率,但可能导致更高的时序挑战。

- **MemoryType**:用户选择适合自己设计的内存类型,这里是DDR3 SDRAM,表示使用的是双倍数据速率(Double Data Rate)三代内存。

- **MemoryPart**:指定具体使用的内存部件型号,如MT41K128M16XX-15E,这影响了数据宽度和其他参数的选择。

- **MemoryVoltage**:根据设计需求设置内存供电电压,此处为1.35V,确保符合DDR3标准。

- **DataWidth**:根据内存部件选择数据宽度,如16位,这是MT41K128M16JT-125支持的典型宽度,用户可以根据实际需求调整。

通过这篇文章,读者能够了解到如何在Xilinx平台上使用MIG IP来有效地管理DDR3内存,并且了解如何配置各个参数以满足特定的性能和延迟要求。这对于理解和实现高效FPGA系统设计至关重要,特别是在处理高速存储器接口时。后续的文章可能会继续探讨如何在硬件设计中集成这个MIG IP,并优化读写控制流程。

2019-03-01 上传

2020-02-17 上传

2022-08-04 上传

2022-08-04 上传

2021-10-04 上传

点击了解资源详情

2021-09-08 上传

禁忌的爱

- 粉丝: 21

- 资源: 334

最新资源

- 奔跑吧蓝色扁平化年终工作总结PPT模板

- phpMyDesktop|arcade-开源

- java毕业设计之springboot摄影跟拍预定管理系统(springboot项目源码+LW+PPT).zip

- matlab导入excel代码-adfasdf2:adfasdf2

- responsimple:一个简单,灵活且响应SwiftCSS网格系统

- hephaestus:AI美术馆

- myAdmin

- phpMedCare-开源

- 简约客厅3D模型效果图

- fastoredis_pro-2.5.0-x86_64.zip

- java毕业设计之springboot医院信管系统(springboot项目源码+LW+PPT+视频).zip

- 蓝色扁平化商务计划PPT模板免费下载

- 发问者:发问者是一个Web应用程序,使用有关主题的问题和答案进行测试以帮助学习。 开发以响应在PC Web浏览器或移动Web浏览器中运行

- 美容整形机构网页模板

- SubscribableEvent:一个简单的强类型pubsubfire事件系统

- 麦杰实时数据库文档V4.0.zip

已收录资源合集

已收录资源合集