Xilinx FPGA设计教程:从Modelsim到Synplify.Pro

需积分: 12 191 浏览量

更新于2024-09-15

收藏 236KB PDF 举报

"Xilinx FPGA设计全流程"

Xilinx的FPGA设计流程涵盖了多个关键步骤,主要涉及仿真、综合、实现和验证。以下是对整个流程的详细解释:

1. Modelsim编译Xilinx库

Modelsim是一款强大的硬件描述语言(HDL)仿真器,用于测试和验证FPGA设计。在开始设计前,需要先编译Xilinx提供的库,以便Modelsim能够识别Xilinx特定的元件和模块。首先,在Modelsim的安装目录下创建一个名为“XilinxLib”的文件夹,并在Modelsim中切换到这个目录。接着,编译“simprims”、“unisims”和“XilinxCoreLib”这三个库,它们位于$Xilinx/verilog/src路径下。通过Modelsim的“Compile”菜单,选择相应的库文件和目标库,即可进行编译。

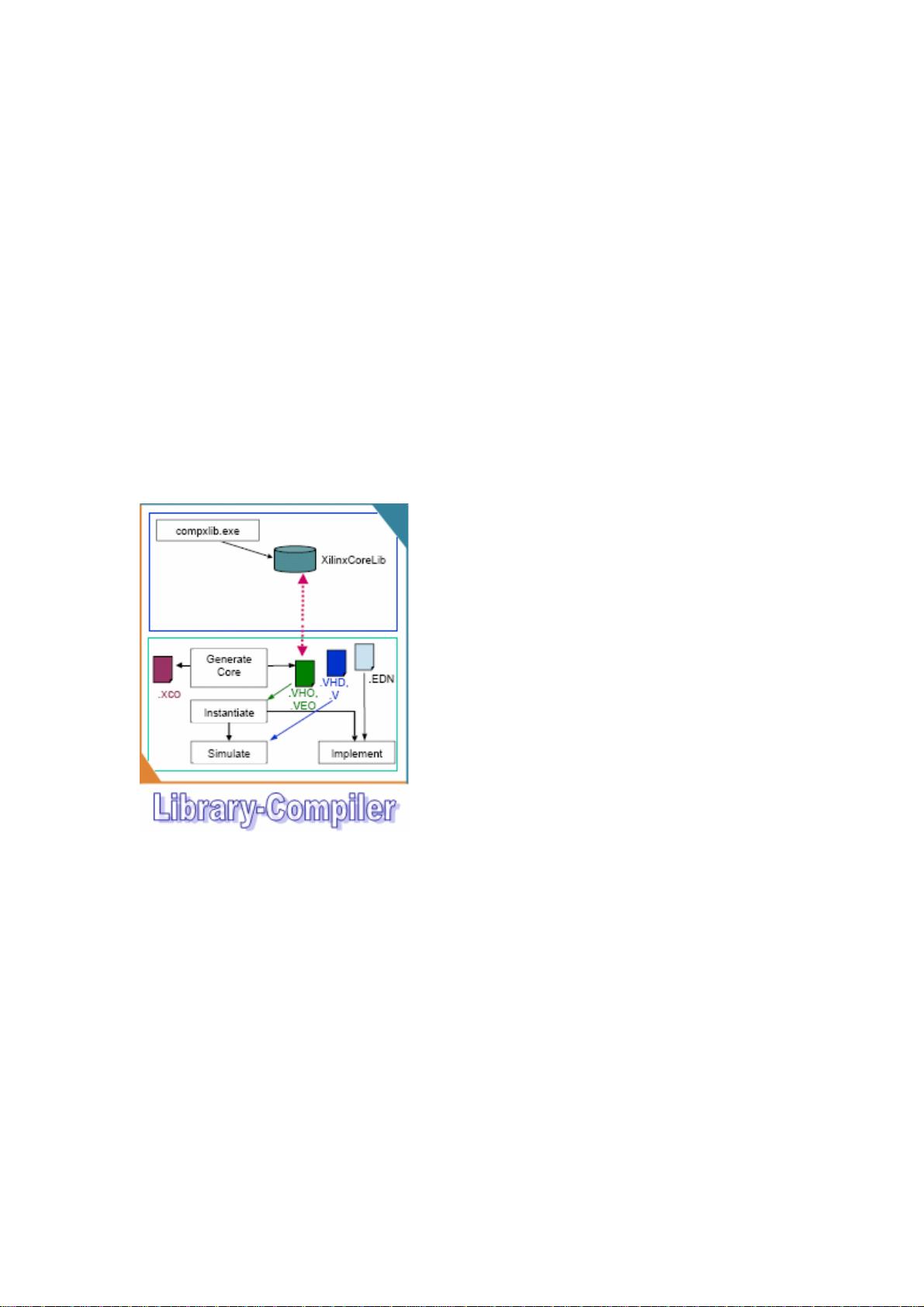

2. 调用Xilinx CORE Generator

CORE Generator是Xilinx提供的一款工具,用于生成参数化和定制化的IP核。不论是通过原理图还是HDL方式,用户都可以使用它来快速构建复杂的设计模块。例如,若需创建一个IP核,首先打开CORE Generator,然后选择或配置所需的IP,该工具会自动生成对应的HDL代码,这些代码可以集成到主设计中。

3. 使用Synplify.Pro综合HDL和内核

Synplify.Pro是一个高级综合工具,它将HDL代码转换成门级网表,适合FPGA的物理实现。在这一阶段,设计者需要将HDL源代码和由CORE Generator产生的IP核输入到Synplify.Pro,进行优化和综合。综合过程考虑了逻辑效率、面积和速度等因素,生成的结果是更适合FPGA架构的逻辑表示。

4. 综合后的项目执行与仿真

经过Synplify.Pro综合后的设计会被导入到Xilinx的集成开发环境ISE中。在ISE中,用户可以进一步配置时序、功耗和布线约束,然后运行Place & Route (P&R)流程,将逻辑门级网表映射到FPGA的物理资源上。完成后,还需要进行功能仿真和时序仿真,确保设计在预期条件下工作正常。

5. 不同类型结构的仿真

仿真在整个设计流程中扮演着关键角色,确保设计在实际运行时能达到预期效果。Modelsim可以进行前仿真和后仿真,前仿真是在综合之前,主要验证逻辑功能;后仿真则在P&R之后,考虑了实际FPGA的延迟和时序特性,更接近实际运行情况。

这个流程对于初学者来说是基础且必要的,理解并掌握这些步骤将有助于成功地完成FPGA设计项目。每个步骤都涉及到不同的工具和技术,熟练掌握它们对于提升设计效率和质量至关重要。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2010-06-11 上传

2008-01-26 上传

2010-07-15 上传

2014-04-13 上传

点击了解资源详情

点击了解资源详情

hudie75

- 粉丝: 0

- 资源: 3

最新资源

- Python中快速友好的MessagePack序列化库msgspec

- 大学生社团管理系统设计与实现

- 基于Netbeans和JavaFX的宿舍管理系统开发与实践

- NodeJS打造Discord机器人:kazzcord功能全解析

- 小学教学与管理一体化:校务管理系统v***

- AppDeploy neXtGen:无需代理的Windows AD集成软件自动分发

- 基于SSM和JSP技术的网上商城系统开发

- 探索ANOIRA16的GitHub托管测试网站之路

- 语音性别识别:机器学习模型的精确度提升策略

- 利用MATLAB代码让古董486电脑焕发新生

- Erlang VM上的分布式生命游戏实现与Elixir设计

- 一键下载管理 - Go to Downloads-crx插件

- Java SSM框架开发的客户关系管理系统

- 使用SQL数据库和Django开发应用程序指南

- Spring Security实战指南:详细示例与应用

- Quarkus项目测试展示柜:Cucumber与FitNesse实践