全数字锁相环中的预置可逆分频器设计与实现

PDF格式 | 606KB |

更新于2024-09-02

| 113 浏览量 | 举报

"该文主要讨论了EDA/PLD中应用于倍频电路的预置可逆分频器设计,通过分析工作原理,推导触发器驱动函数,并利用simulink和FPGA构建分频器模型,实现了预置模和可逆分频功能,满足全数字锁相环的需求。文中提到了传统锁相环与全数字锁相环的区别,并指出全数字锁相环对分频器的特殊要求。此外,还介绍了变模可逆分频器的工作原理,包括触发器的控制逻辑和状态转换过程。"

在电子设计自动化(EDA)和可编程逻辑器件(PLD)领域,倍频电路是重要的频率合成技术之一,常用于通信、雷达和测试设备等领域。预置可逆分频器在全数字锁相环(DLL)中扮演着关键角色,其性能直接影响锁相环的稳定性和频率精度。传统的锁相环主要由模拟组件构成,而全数字锁相环则完全由数字组件如数字鉴相器、数字环路滤波器、压控振荡器和分频器等组成,从而实现更高的精度和更灵活的设计。

分频器作为锁相环的一部分,其主要任务是将输入信号按照预定的比例进行分频。在全数字锁相环中,分频器不仅要能够预设分频模数,还需要具备可逆分频的能力,即能够实现增加或减少计数的操作,以适应不同应用场景的需求。为了解决这一问题,文章提出了一种基于simulink和FPGA的分频器设计方法,通过建立模型并进行实验验证,证明了该设计能够有效实现预置模和可逆分频功能。

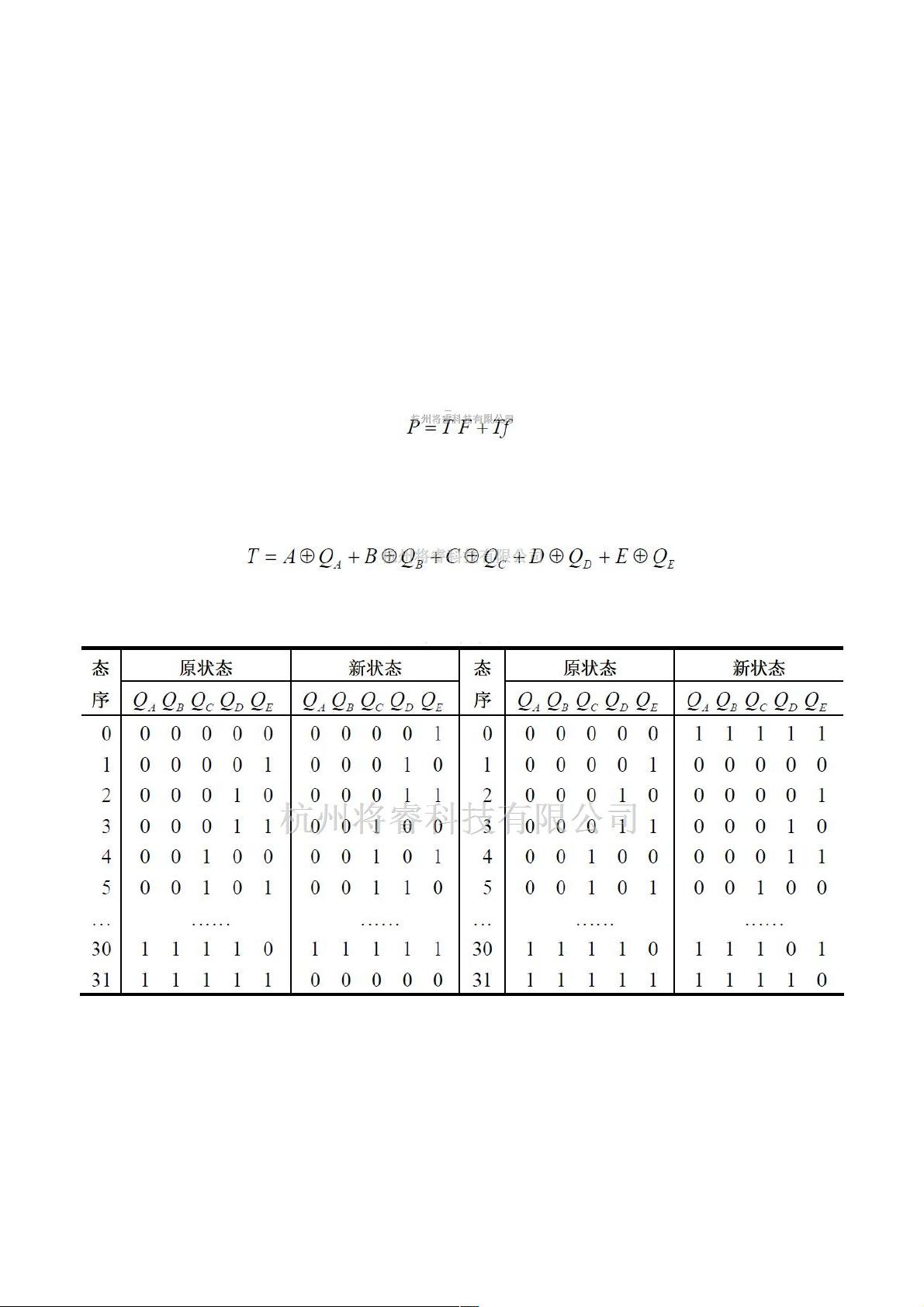

变模可逆分频器的核心在于控制逻辑的设计,包括正常控制函数f和强迫控制函数F,以及符合函数T。在正常工作模式下,触发器的更新由卡诺图决定的f函数控制;当符合函数T为1时,触发器不受F影响,按常规方式进行分频;而在T为0时,F起作用,使得分频器能够跳转到预设的状态。这样的设计允许分频器在维持周期性计数的同时,也能在任意时刻改变计数方向,从而实现可逆分频。

通过状态转换表(如表1所示),可以直观地看到分频器在递增和递减分频时的状态变化,而计数值与触发器当前值的关系(如表2所示)则揭示了分频器内部计数状态与实际输出之间的映射。这样的设计灵活性高,能够适应多种复杂的频率合成需求。

该文通过深入研究和实验证明,基于EDA/PLD的预置可逆分频器设计不仅满足了全数字锁相环的高精度要求,也提供了灵活的频率调整能力,对于提升系统性能具有重要意义。这种设计方法为现代高频电子系统中的频率合成提供了新的解决方案。

相关推荐

weixin_38705640

- 粉丝: 8

最新资源

- Ruby语言集成Mandrill API的gem开发

- 开源嵌入式qt软键盘SYSZUXpinyin可移植源代码

- Kinect2.0实现高清面部特征精确对齐技术

- React与GitHub Jobs API整合的就业搜索应用

- MATLAB傅里叶变换函数应用实例分析

- 探索鼠标悬停特效的实现与应用

- 工行捷德U盾64位驱动程序安装指南

- Apache与Tomcat整合集群配置教程

- 成为JavaScript英雄:掌握be-the-hero-master技巧

- 深入实践Java编程珠玑:第13章源代码解析

- Proficy Maintenance Gateway软件:实时维护策略助力业务变革

- HTML5图片上传与编辑控件的实现

- RTDS环境下电网STATCOM模型的应用与分析

- 掌握Matlab下偏微分方程的有限元方法解析

- Aop原理与示例程序解读

- projete大语言项目登陆页面设计与实现