等精度测频原理频率计程序与仿真分析

需积分: 10 2 浏览量

更新于2024-10-20

1

收藏 172KB DOC 举报

"8.17 采用等精度测频原理的频率计程序与仿真"

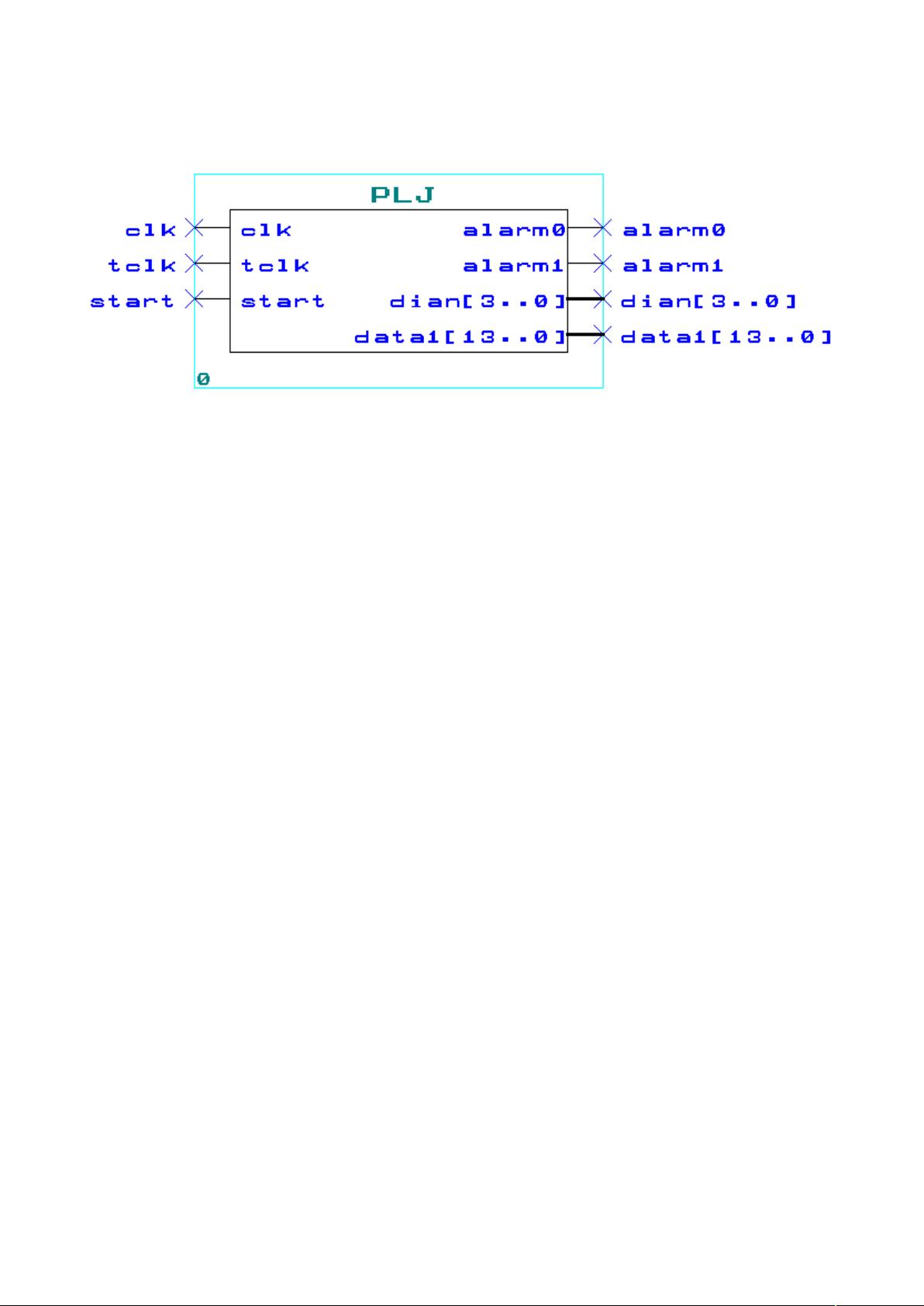

本文档介绍了一个基于等精度测频原理的频率计程序,用于4位显示的频率测量。该程序用VHDL语言编写,适用于数字系统中的频率测量,能够检测并显示输入信号的频率。程序文件名为PLJ.vhd,最后更新日期为2004年4月14日。

在等精度测频原理中,频率计通过比较两个时钟周期来确定被测信号的频率。这里的基准时钟为10KHz,被测信号(tclk)的频率将与基准时钟进行比较。程序设计包含以下几个关键部分:

1. **预置闸门(Preset Gate)**:预置闸门计数器(q)以基准时钟(clk)为时钟源,其范围设定为0到9999。当接收到复位信号(start)时,计数器清零,预置闸门关闭。当计数器达到9999时,预置闸门再次关闭,确保每次测量周期的精确性。

2. **实际闸门(Actual Gate)**:实际闸门计数器(q1)根据被测信号(tclk)的上升沿计数。只有在预置闸门开启(en='1')时,q1才进行计数。这使得在每个测量周期内,只对一定数量的被测信号脉冲进行计数。

3. **基准信号计数器(Reference Counter)**:基准信号计数器(q2)同样由基准时钟(clk)驱动,范围为0到20000。这个计数器用于计算基准时钟的周期,以确保测量精度。

4. **运算器(Calculator)**:运算器(qq, qqq)用于计算频率数据,它会根据q1和q2的值进行计算,以确定被测信号相对于基准时钟的频率比例。

5. **显示输出**:频率数据(data1)和小数点(dian)的输出,用于显示频率值。此外,还有超量程(alarm0)和欠量程(alarm1)的输出,用于指示测量结果是否超出预设范围。

整个程序的架构遵循VHDL的行为描述方式,使用了两个并行进程,分别处理基准时钟和被测信号的事件。通过这样的设计,频率计能够实现等精度测量,即在每个测量周期内,被测信号的计数与基准时钟的计数具有相同的相对精度。

这个频率计程序是数字系统中进行频率测量的一个实例,它利用等精度测频方法确保了测量的准确性和一致性。通过VHDL实现,可以方便地在FPGA或ASIC上进行硬件仿真和部署。

2024-05-26 上传

1549 浏览量

275 浏览量

2024-12-03 上传

358 浏览量

2024-10-27 上传

219 浏览量

292 浏览量

tandyyang

- 粉丝: 1

- 资源: 49

最新资源

- oracle9i ocp认证资料

- ——————编程之道

- FAT32文件系统详细介绍

- Statspack-v3.0.pdf

- —————— C#数据结构和算法

- 线性代数同济四版答案

- Web Application Development Using Python and Zope Components

- 设计模式和设计原则,模式设计使用方式

- DB2工作手册,IBM官方

- mega16的芯片资料

- avr单片机系列mega8的芯片资料

- 中兴面试--公共部分中兴面试--公共部分

- URTracker案例介绍

- 程序员的SQL金典 程序员的SQL金典

- 利用UUP实现Portal和LDAP同步用户信息.doc

- 多路开关 cd4051中文资料