FPGA实现的DDR+SDRAM控制器设计

需积分: 10 139 浏览量

更新于2024-09-13

收藏 575KB PDF 举报

"基于FPGA的DDR+SDRAM控制器设计与实现"

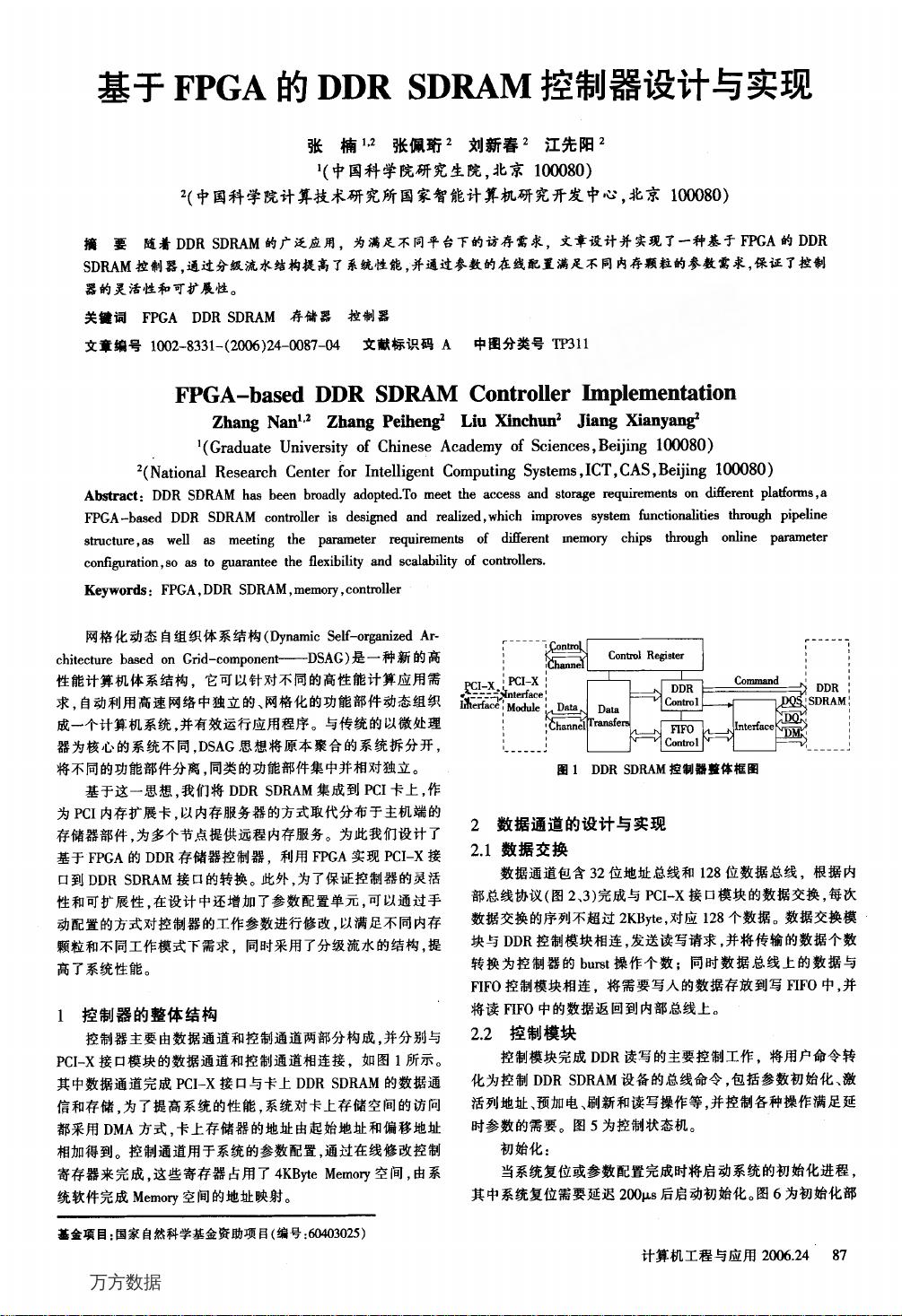

本文主要探讨了如何设计和实现一个基于FPGA(Field-Programmable Gate Array,现场可编程门阵列)的DDR SDRAM(Double Data Rate Synchronous Dynamic Random-Access Memory,双倍数据速率同步动态随机存取内存)控制器。DDR SDRAM在现代电子系统中被广泛采用,因其高速、低延迟的特性,尤其适用于需要大量数据传输和处理的应用。设计这样一个控制器的主要目的是满足不同平台下的内存访问和存储需求。

首先,文章强调了控制器的设计是通过采用分级流水线结构来提高系统性能。流水线技术是一种常见的硬件优化方法,它将复杂的操作分解成多个阶段,每个阶段在一个独立的硬件单元中同时进行,从而提高了处理速度。在DDR SDRAM控制器中,这种流水线结构能够使得数据读写操作并行进行,减少了等待时间,显著提升了内存访问效率。

其次,为了适应不同类型的DDR SDRAM芯片,该控制器支持在线参数配置。不同的内存颗粒可能具有不同的工作频率、时序参数等,通过参数的在线配置,控制器能够灵活地适应这些差异,确保与各种内存芯片的兼容性。这种灵活性和可扩展性对于系统设计来说至关重要,因为它允许控制器在不更改硬件的前提下,适应未来可能出现的新型内存技术。

此外,文章还可能涉及以下知识点:

1. **FPGA的优势**:FPGA相比ASIC(Application-Specific Integrated Circuit,特定应用集成电路)具有设计灵活、快速原型验证、可重配置等优点,使其成为实现高性能、可定制化控制器的理想选择。

2. **DDR SDRAM的工作原理**:包括其数据传输机制、预充电、行地址选通、列地址选通等操作,以及如何通过时钟边沿的双倍数据传输率来提升性能。

3. **时序分析和约束**:设计DDR SDRAM控制器时,必须考虑严格的时序要求,如CAS(Column Address Strobe,列地址选通信号)延迟、RAS(Row Address Strobe,行地址选通信号)延迟、时钟周期和数据有效窗口等。

4. **错误检测和纠正**:控制器可能包含ECC(Error Correction Code,错误校验码)或其他错误检测机制,以确保数据的完整性。

5. **接口设计**:控制器需要与CPU或其他系统组件进行通信,因此会涉及到AXI(Advanced eXtensible Interface)、AHB(Advanced High-performance Bus)或其他总线协议的接口设计。

6. **测试与验证**:设计完成后,通常会使用仿真工具进行功能验证,以及使用硬件描述语言(如VHDL或Verilog)进行逻辑综合和时序分析,以确保控制器的正确性和可靠性。

文章详细阐述了一个基于FPGA的DDR SDRAM控制器的设计过程,包括了提高系统性能的关键技术和满足内存兼容性的策略,为读者提供了深入理解此类控制器设计的宝贵资料。

2021-10-28 上传

2023-05-12 上传

2023-05-10 上传

2023-09-01 上传

2024-08-10 上传

2023-09-07 上传

2023-07-27 上传

2023-05-30 上传

2023-07-23 上传

河滨南燕

- 粉丝: 0

- 资源: 2

最新资源

- Google Test 1.8.x版本压缩包快速下载指南

- Java实现二叉搜索树的插入与查找功能

- Python库丰富性与数据可视化工具Matplotlib

- MATLAB通信仿真设计源代码与应用解析

- 响应式环保设备网站模板源码下载

- 微信小程序答疑平台完整设计源码案例

- 全元素DFT计算所需赝势UPF文件集合

- Object-C实现的Flutter组件开发详解

- 响应式环境设备网站模板下载 - 恒温恒湿机营销平台

- MATLAB绘图示例与知识点深入探讨

- DzzOffice平台新插件:excalidraw白板功能介绍与使用指南

- Java基础实训教程:电子商城项目开发与实践

- 物业集团管理系统数据库设计项目完整复刻包

- 三五族半导体能带参数计算器:精准模拟与应用

- 毕业论文:基于SSM框架的毕业生跟踪调查反馈系统设计与实现

- 国产化数据库适配:人大金仓与达梦实践教程