FPGA配置方式解析:AS、PS与JTAG

需积分: 20 13 浏览量

更新于2024-08-31

1

收藏 826KB PDF 举报

"FPGA器件的配置下载方式包括主动配置(AS)、被动配置(PS)以及JTAG方式。AS模式下,FPGA在上电时作为控制器,从外部存储器读取数据并同步到FPGA中;PS模式由外部控制器通过配置器件完成,将数据写入FPGA;JTAG模式则通过标准测试接口进行编程,但断电后需要重新烧录。对于Cyclone系列器件,通常支持AS和JTAG两种方式,AS用于下载.pof文件到EPCS**,JTAG用于下载.sof文件到SRAM。生成.pof文件需在QuartusII中设置并重新编译,然后通过programmer工具进行下载。"

在FPGA设计中,配置下载方式的选择至关重要,因为它直接影响到程序的加载速度、稳定性和可维护性。FPGA的三类配置下载方式各有特点:

1. 主动配置方式(AS,Activeserialconfigurationmode):在这种模式下,FPGA自身在上电后成为配置过程的控制器。它控制外部存储器(如EPCS**)并发送读取数据信号,数据通过FPGA_DATA0引脚以FPGA_DCLK时钟同步的方式逐位传入,实现器件的编程。AS模式的一个优势是程序可以长期保存,即使断电后也能在下次上电时自动加载。

2. 被动配置方式(PS,Passiveserialconfigurationmode):与AS不同,PS模式下,配置过程由外部设备(如计算机或控制器)控制。EPCS器件作为控制设备,将数据写入FPGA,实现在线编程。这种方式允许对FPGA进行动态更新,但通常需要外部控制设备的支持。

3. JTAG(JointTestActionGroup)模式:JTAG是一种通用的边界扫描测试标准,常用于硬件测试和编程。在FPGA中,JTAG可以将.sof文件(Intermediate Functional Representation)直接烧录到内部的SRAM中。然而,由于SRAM是非易失性存储,断电后程序会丢失,因此每次上电都需要重新烧录。

在实际应用中,AS和JTAG结合使用的情况很常见。开发阶段可以利用JTAG方便地进行调试和修改,完成后使用AS模式将程序固化到配置芯片,确保上电后程序的稳定运行。如果AS模式出现问题,可以通过JTAG生成.jic文件,用于检查和确认配置芯片的状态。

生成.jic文件的步骤通常涉及以下几点:

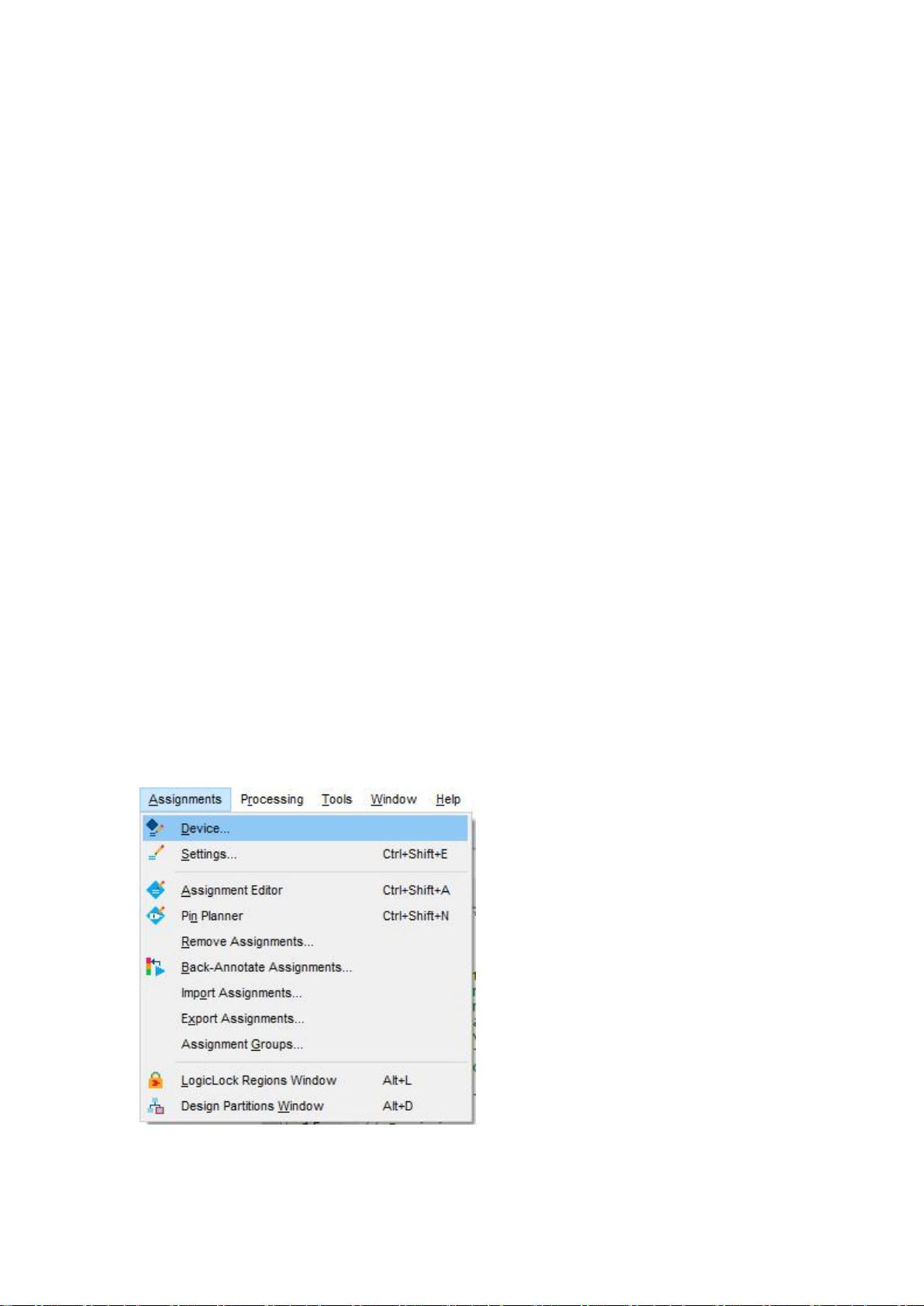

1. 在QuartusII软件中,完成工程的设计、编译和引脚分配。

2. 进入“Device and Pin Options”设置,选择“Active Serial Programming”模式。

3. 编译工程以生成.pof文件。

4. 在programmer工具中,勾选“Program/Configure”,选择.start开始下载。

5. 下载完成后,将板子上的模式切换回正常运行状态,以保持程序在下次上电时能够运行。

理解并熟练掌握FPGA的不同配置方式对于开发和维护FPGA系统至关重要,可以根据项目需求灵活选择合适的配置方案。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2011-11-20 上传

2020-08-14 上传

2011-10-29 上传

2020-10-15 上传

2021-02-03 上传

2021-10-11 上传

weixin_39992374

- 粉丝: 0

- 资源: 16

最新资源

- 单片机MCS-51系列指令快速记忆法

- S2410核心板原理图

- A planar four-port channel drop filter in the three-dimensional woodpile photonic crystal

- 计算机视觉方面的一些内容

- 交通灯控制器的VHDL设计

- 2009年软件设计师下午题预测题

- PLSQL中的多进程通信技术.doc

- 物流管理系统之毕业设计

- 一元多项式的基本运算

- 毕业设计大礼包直流电动机控制系统 声控小车

- Matlab图形用户界面编程_中文参考手册

- C#简明教程(简单明了,适合初学者)

- 2006年考研英语真题

- GDB完全手册-很简单的

- 《C++Template》(侯捷)

- ActionScript_3.0_Cookbook_中文版