Verilog语言入门:基础语法与模块设计解析

需积分: 6 71 浏览量

更新于2024-07-31

收藏 410KB PPT 举报

"本资源主要介绍了Verilog设计的基础知识,包括Verilog的起源、发展、基本语法以及在数字系统设计中的应用。通过学习,读者将能够掌握Verilog程序的架构和语言要素,对比硬件描述语言与软件编程语言的差异,并了解如何使用Verilog进行简单的设计实例。"

Verilog是一种广泛应用于数字电子系统设计的硬件描述语言(HDL),由Phil Moorby于1983年创建。随着GDA公司的被Cadence收购以及Verilog-XL仿真器的成功,Verilog逐渐流行起来,并在1995年成为IEEE 1364-1995标准,后来又有Verilog-2001标准的发布,被多数现代工具所支持。

学习Verilog的目标是理解和建立数字系统设计的概念,以及掌握其程序结构和基本语法。学习重点在于理解Verilog程序的整体架构,如模块的定义和使用,以及语言的基本要素。

5.1 Verilog简介中,讲解了Verilog的历史和发展,强调了它在数字系统设计中的重要性。Verilog不仅用于描述硬件,还支持行为级和混合级建模,使得设计者能以更抽象的层次进行设计。

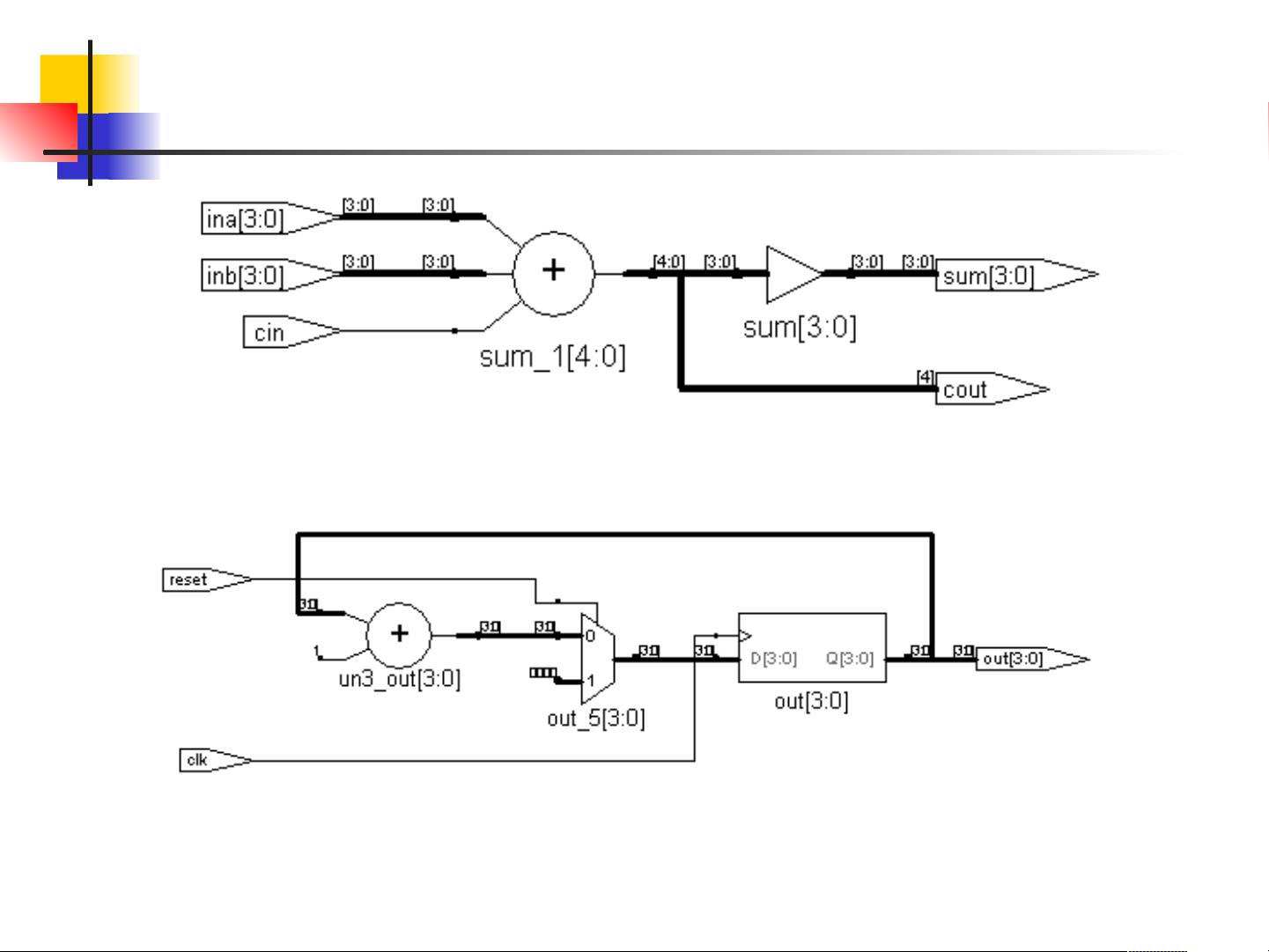

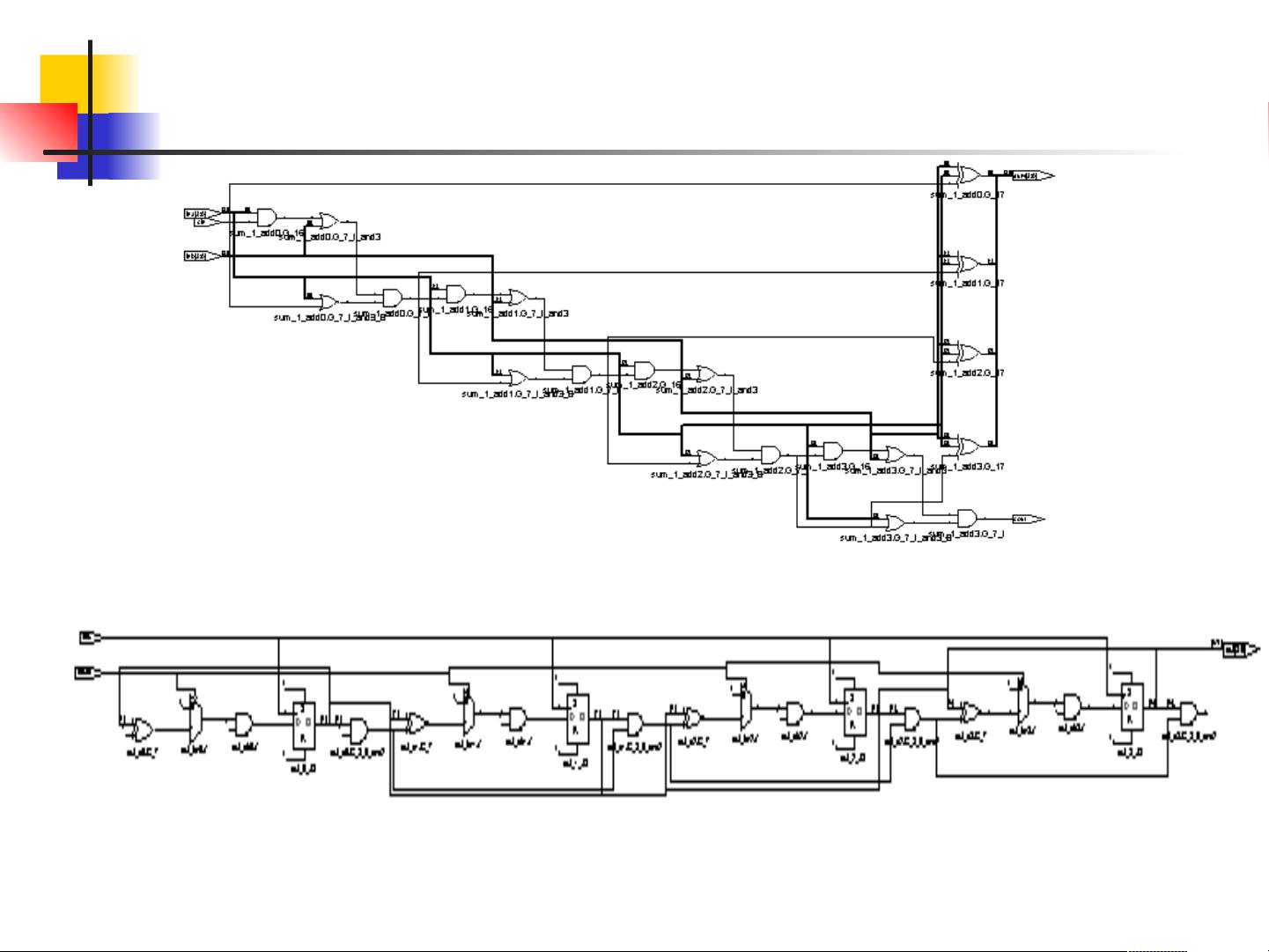

5.2 Verilog设计举例部分,通常会通过实例来展示如何使用Verilog编写一个简单的电路,如4位全加器。模块是Verilog中的基本单元,包含了输入、输出和内部逻辑。在例1中,`adder4`模块接收4位输入`ina`和`inb`,一位进位输入`cin`,并输出4位和`sum`及一位进位输出`cout`。逻辑功能通过`assign`语句定义,实现了全加器的功能。

5.3 Verilog模块的结构解释了模块的组成部分,包括模块声明、端口列表、变量声明和逻辑操作。

5.4 Verilog语言要素涵盖了关键字、数据结构和控制流等元素,这些都是编写Verilog代码的基础。

5.5常量是指在设计中不会改变的值,它们可以是数值或字符串,常用于配置参数。

5.6数据类型包括基本类型(如reg、integer、real等)和向量类型,向量可以表示多位数值。

5.7参数是可编程的常量,允许在设计时或编译时设置,提高了设计的灵活性。

5.8向量是Verilog中表示多位数据的机制,可以是二进制、八进制、十进制或十六进制表示。

5.9运算符包括逻辑、算术、比较和位操作等,它们用于构建复杂的逻辑表达式。

学习Verilog还需要对比硬件描述语言和软件编程语言,例如C语言,理解两者的区别在于Verilog描述的是硬件的并行行为,而C语言则遵循顺序执行的规则。

总结来说,Verilog是设计数字系统的强大工具,通过学习其基本概念、语言结构和操作符,设计师能够有效地描述和验证数字电路。同时,理解Verilog与其他编程语言的差异,有助于更好地适应硬件设计的思维方式。

cxl1419

- 粉丝: 1

- 资源: 10

最新资源

- 网络游戏-基于极大团发现的网络热点话题检测方法及装置.zip

- 海上钻井平台PPT模板

- VBIC卡管理系统(源代码+论文+外文翻译+答辩PPT).zip

- Cookie AutoDelete-crx插件

- pixel-scaling:使用GLSL中的hqx滤镜进行像素缩放

- leetcode答案-leets:leetcode问题的解决方法和解释

- my-calculator

- GitHub加速-crx插件

- javaone2015-cloudone:JavaOne 2015演示文稿的示例项目-“其他会话”。 主要目标是详细说明云解决方案中基于REST的集成模式

- 钻机采油背景的中石油PPT模板

- 易语言-远程服务支持库2.0#0版

- Download with Ant Download Manager-crx插件

- 基于文本挖掘的企业隐患排查质量分析数据集.zip

- PROYECTO:ARCHIVO DE TRABAJOS

- 绿色化学实验PPT模板

- Kubach:Kubach.TK服务器的启动器