FPGA设计:门控时钟的利弊与替代策略

在FPGA设计中,时钟分析是一项关键任务,尤其是在处理门控时钟(gate clock)的问题上。门控时钟并非FPGA设计的理想选择,尽管在ASIC中,通过门控时钟可以有效降低功耗,但在FPGA环境中,其可能导致诸如毛刺(glitches)、时延偏移(skew)和抖动(jitter)等时序问题。这些问题会直接影响电路的性能和可靠性。

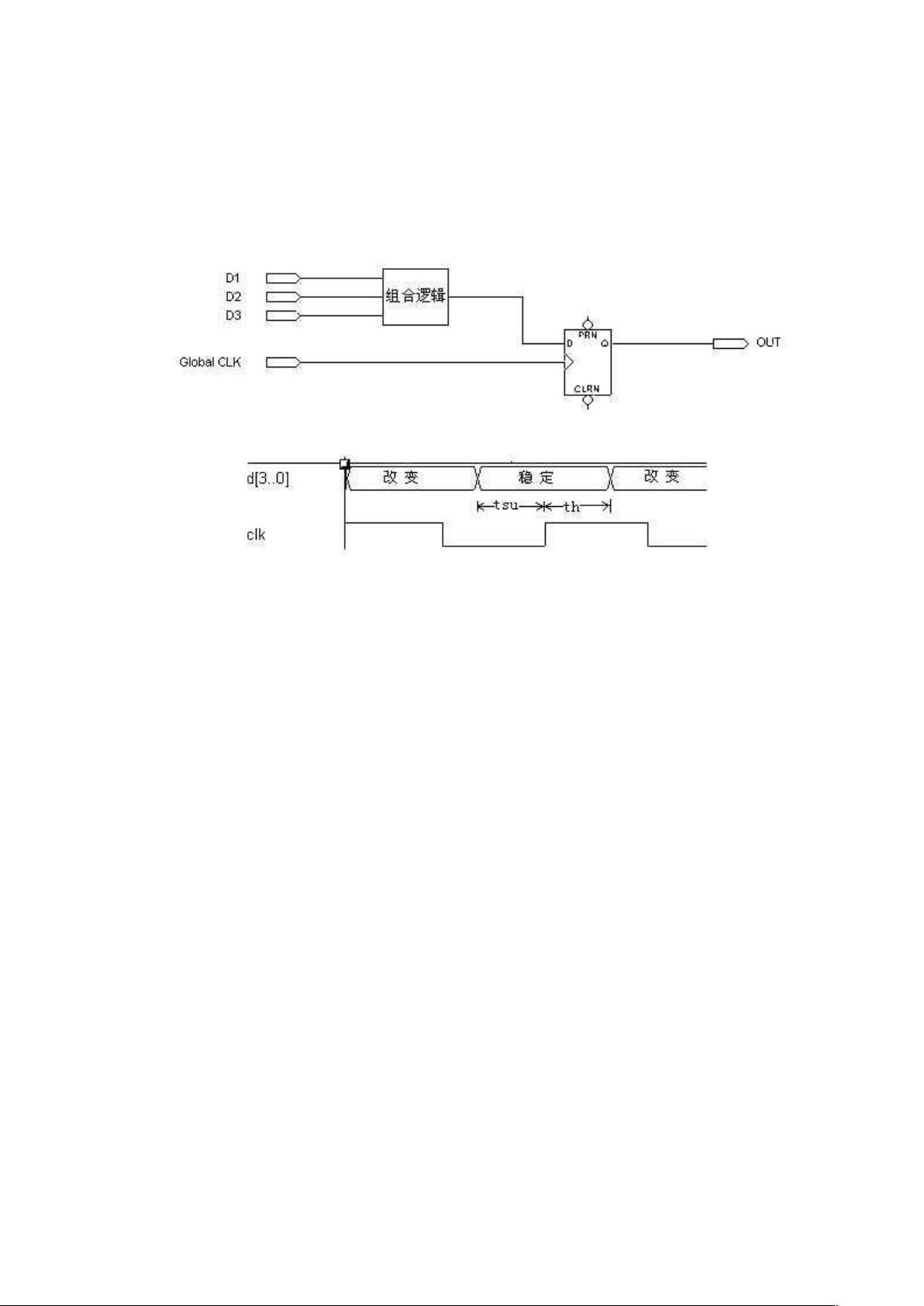

首先,门控时钟的“门控”特性意味着一个时钟信号受到其他非时钟信号的逻辑控制,例如在一个与门(AND gate)中,控制信号决定了CLK何时启用。然而,这可能导致逻辑竞态条件,特别是在复杂的电路结构中,额外的逻辑可能会在时钟信号的边缘触发,产生不必要的毛刺。为了避免这种现象,驱动门控时钟的逻辑必须仅包含一个与门或或门,所有其他输入应视为地址或控制线,遵守严格的建立和保持时间约束。

尽管门控时钟在某些情况下能够节省动态功耗,但这不符合同步设计原则。使用使能时钟(enable clock)作为替代方案可以避免这个问题,因为它在使能信号关闭时停止时钟活动。然而,使能时钟并不能像门控时钟那样完全停掉时钟,这意味着它无法提供相同的功耗节省。Altera提供的解决方案是在上升沿有效的系统时钟clk下降沿时先延迟门控时钟,然后通过与使能信号结合,形成更为稳定的门控时钟源。

这种方法确实有助于减少毛刺和亚稳态的影响,但如果系统时钟的占空比不稳定,或者使能信号和时钟信号之间的逻辑关系过于复杂,就会对电路的功能和时序性能产生负面影响。因此,设计者在采用门控时钟电路时,必须精细调整时钟占空比以及门控逻辑的复杂度,确保整体设计的稳健性和效率。

FPGA设计者在使用门控时钟时需格外谨慎,以确保电路的性能、功耗和可靠性。遵循严格的时序规则,理解不同时钟控制策略的优缺点,并在必要时寻求专门的优化技术,如Altera的解决方案,是确保成功设计的关键。同时,持续的时序分析(STA)在整个设计过程中至关重要,以便及时发现并解决潜在问题。

2021-07-13 上传

183 浏览量

2018-08-18 上传

2023-09-30 上传

2023-07-07 上传

2023-07-22 上传

2023-07-14 上传

2023-08-18 上传

2023-08-17 上传

loves6036

- 粉丝: 1

- 资源: 14

最新资源

- 彩虹rain bow point鼠标指针压缩包使用指南

- C#开发的C++作业自动批改系统

- Java实战项目:城市公交查询系统及部署教程

- 深入掌握Spring Boot基础技巧与实践

- 基于SSM+Mysql的校园通讯录信息管理系统毕业设计源码

- 精选简历模板分享:简约大气,适用于应届生与在校生

- 个性化Windows桌面:自制图标大全指南

- 51单片机超声波测距项目源码解析

- 掌握SpringBoot实战:深度学习笔记解析

- 掌握Java基础语法的关键知识点

- SSM+mysql邮件管理系统毕业设计源码免费下载

- wkhtmltox下载困难?找到正确的安装包攻略

- Python全栈开发项目资源包 - 功能复刻与开发支持

- 即时消息分发系统架构设计:以tio为基础

- 基于SSM框架和MySQL的在线书城项目源码

- 认知OFDM技术在802.11标准中的项目实践