Verilog实现:同步与异步FIFO设计及低功耗技术解析

需积分: 50 129 浏览量

更新于2024-09-03

收藏 288KB PDF 举报

"asyn-syn-fifo.pdf 包含了关于Verilog语言在实现异步和同步fifo时常见的错误,以及数字集成电路设计流程、低功耗技术、MOS管的工作原理和FPGA中的查找表(LUT)原理等主题。文档提供了作者自己编写的同步fifo和异步fifo的源代码作为示例。同步fifo的Verilog代码展示了如何管理读写地址、空满标志的检测,以及读写计数器的更新。"

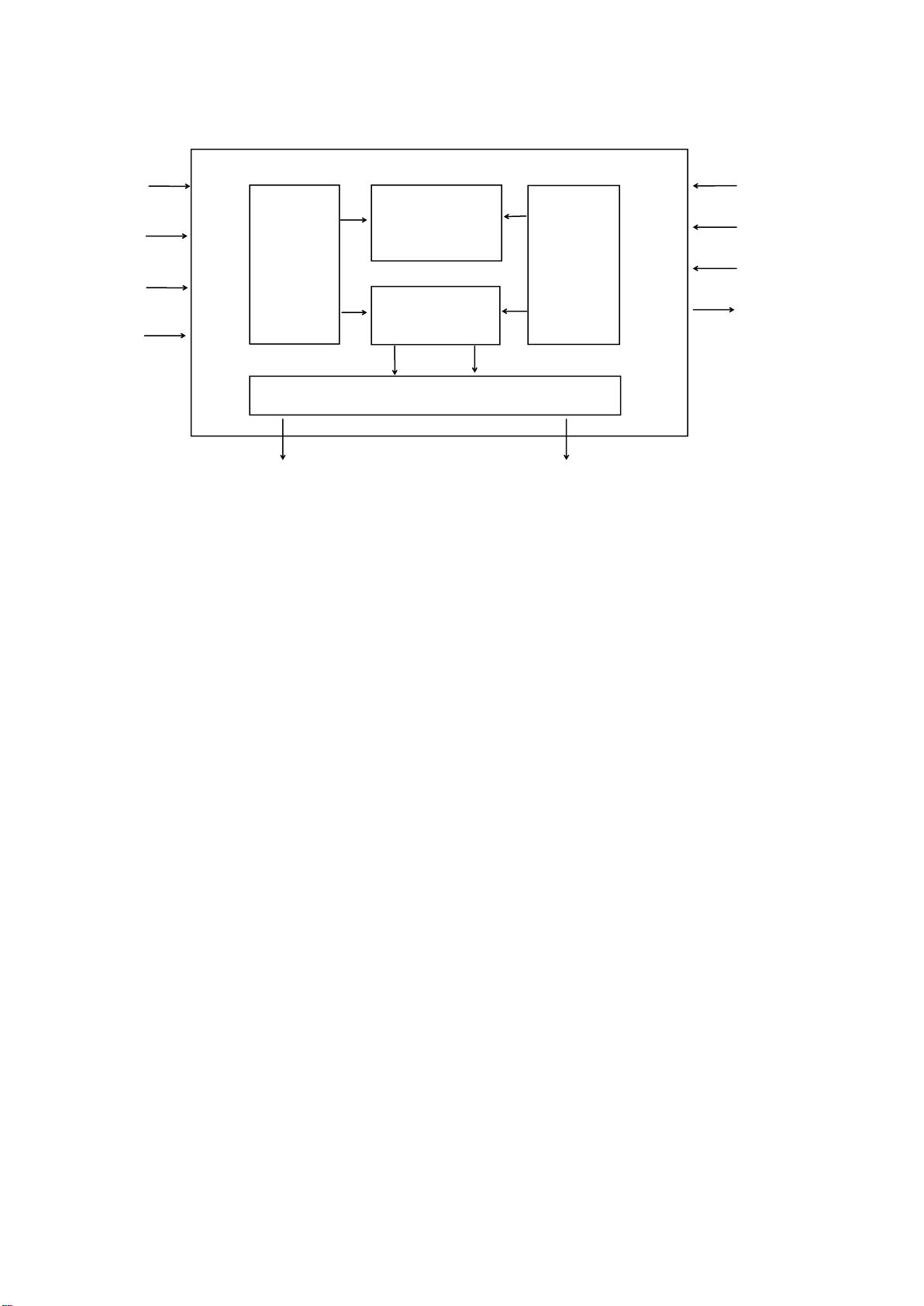

在数字集成电路设计中,FIFO(First In First Out,先进先出)存储器常用于数据缓冲,特别是在处理高速数据流和不同时钟域之间的通信时。同步FIFO和异步FIFO的主要区别在于它们如何处理时钟信号。同步FIFO通常在同一个时钟域内工作,而异步FIFO则涉及两个或更多不同的时钟域。

同步FIFO的Verilog代码段中,`syn_fifo`模块是核心部分,它包含了以下关键组件:

1. **读写地址管理**:`waddr`和`raddr`寄存器分别用于跟踪写入和读取位置。在时钟沿,它们会根据读写使能信号(`ren`和`wen`)进行更新。当读写操作同时进行且未达到满或空状态时,会特别注意避免“读写冲突”。

2. **空满标志计算**:`rempty`和`wfull`信号用于指示FIFO是否为空或已满。这些标志通过读写计数器`rdata_cnt`的值来确定,当计数器等于0时,表示FIFO为空;当计数器达到预设的最大值(如8'hff,表示8个数据项)时,表示FIFO已满。

3. **读写计数器更新**:根据`write_only`和`read_only`的逻辑,`rdata_cnt`会相应增加或减少。这两个信号通过组合逻辑来决定是否允许计数器改变。

4. **FifoMem模块**:这是实际的内存存储单元,使用了参数化的数据宽度`DSIZE`和地址宽度`ASIZE`。它接收读写操作的时钟、复位、使能、数据及地址信号,并提供读写数据和空满标志。

5. **Fifo空满控制模块**:这部分逻辑确保在读写操作时正确处理FIFO的状态,防止数据丢失或错误读取。

此外,文档还提到了数字IC设计流程,这通常包括前端设计(逻辑综合、时序分析)、后端设计(布局布线、物理验证)和版图设计。低功耗技术涉及在设计阶段就考虑电源管理和功耗优化,如多电压域、动态电压频率调整(DVFS)等。MOS管(金属-氧化物-半导体场效应晶体管)是集成电路中的基本构建块,控制电流通过半导体的通道。FPGA中的查找表(LUT)是一种可编程逻辑元件,可以配置为实现任意布尔函数,是FPGA实现逻辑功能的基础。

这份文档提供了深入理解Verilog实现FIFO及其在数字IC设计中应用的宝贵资源。通过学习这些代码和概念,设计师能够更好地掌握如何在实际项目中构建高效、可靠的FIFO解决方案。

250 浏览量

2022-07-15 上传

232 浏览量

2021-08-11 上传

199 浏览量

186 浏览量

135 浏览量

落雨无风

- 粉丝: 297

最新资源

- 昆仑通态MCGS嵌入版_XMTJ温度巡检仪软件包解压教程

- MultiBaC:掌握单次与多次组批处理校正技术

- 俄罗斯方块C/C++源代码及开发环境文件分享

- 打造Android跳动频谱显示应用

- VC++实现图片处理的小波变换方法

- 商城产品图片放大镜效果的实现与用户体验提升

- 全新发布:jQuery EasyUI 1.5.5中文API及开发工具包

- MATLAB卡尔曼滤波运动目标检测源代码及数据集

- DoxiePHP:一个PHP开发者的辅助工具

- 200mW 6MHz小功率调幅发射机设计与仿真

- SSD7课程练习10答案解析

- 机器人原理的MATLAB仿真实现

- Chromium 80.0.3958.0版本发布,Chrome工程版新功能体验

- Python实现的贵金属追踪工具Goldbug介绍

- Silverlight开源文件上传工具应用与介绍

- 简化瀑布流组件实现与应用示例