Verilog HDL深度学习:从入门到综合优化

"这是一份全面的Verilog教程,涵盖了从基础到高级的多个方面,旨在教授数字集成电路设计,特别是使用Verilog硬件描述语言(HDL)进行设计、仿真和综合。教程由北大微电子学系的专家于敦山教授编写,内容丰富,包括Verilog的应用、语言构成、结构级与行为级描述、延时处理、测试平台搭建、设计验证、Cadence Verilog仿真器的使用、逻辑综合、设计约束、优化以及自动布局布线等关键概念。此外,还包含了实验实践和相关参考书籍,适合初学者和进阶者学习。"

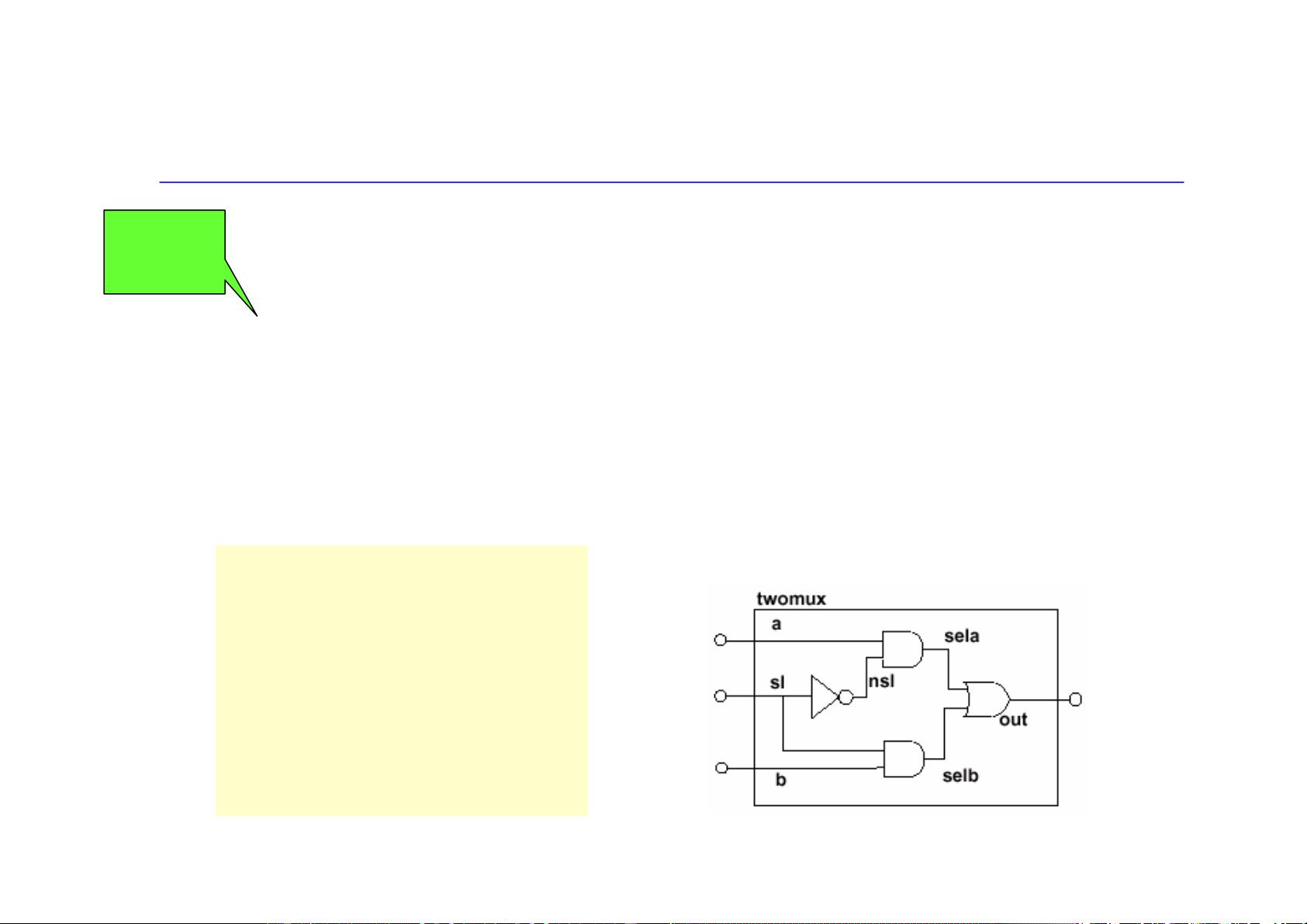

在本教程中,首先介绍了Verilog HDL的基础知识,包括其在数字集成电路设计中的应用、语言的基本构成元素,如模块、变量、操作符等。讲解了结构级描述,用于描述电路的物理连接,以及行为级描述,用于描述电路的功能行为。同时,详细阐述了延时的特点,这对于理解数字系统的时序至关重要。Verilogtestbench的介绍则帮助学习者掌握如何建立和运行测试平台,以验证设计的正确性。

课程进一步深入到Cadence Verilog仿真器的使用,包括设计的编译、仿真流程,以及如何利用源库进行设计管理。提供了两种调试方法:命令行界面和图形用户界面(GUI),使学习者能够适应不同的工作环境。延时的计算和反标注是性能仿真描述的重要部分,有助于优化设计性能。

在逻辑综合部分,教程介绍了设计对象、静态时序分析(STA)和可综合的HDL编码风格,为后续的硬件实现打下基础。设计约束的设置是确保设计满足特定性能指标的关键,而设计优化包括设计编译和有限状态机(FSM)的优化,以提高效率和减少资源消耗。

实验部分强调了实际操作,通过实践来巩固理论知识,涉及Verilog设计、综合和布局布线等环节。最后,教程简要介绍了自动布局布线工具Silicon Ensemble,这是实现芯片物理设计自动化的重要工具。

参考书籍包括了 Cadence Verilog Language and Simulation、Verilog-XL Simulation with Synthesis 和 Envisia Ambit Synthesis,以及刘明业等翻译的《硬件描述语言Verilog》,这些书籍提供了深入学习Verilog的额外资源。

这份教程覆盖了Verilog学习的全过程,从理论到实践,为有意从事数字集成电路设计的工程师或学生提供了全面的学习路径。

2620 浏览量

2008-11-06 上传

2010-07-19 上传

127 浏览量

559 浏览量

295 浏览量

qq_27149269

- 粉丝: 0

最新资源

- Java搜索引擎指南:Lucene实战

- Windows设备驱动开发详解

- Oracle DBA在Unix下的命令参考手册

- SOA深度解析:架构、价值与构建技术

- ActiveReports实战教程:从入门到精通

- 优化ASP.Net性能:十大技巧解析

- C#数据库备份与恢复关键代码实现

- 国际开源大师齐聚北京:2008 Linux开发者研讨会

- ArcGIS二次开发实战指南

- 《开源》创刊:见证中国开源生态的崛起与转型

- Eclipse常用快捷键全解析:提升开发效率必备

- 使用Java将JTable数据导出到Excel

- 通用扑克牌程序源代码:数据结构与操作

- TortoiseSVN客户端安装与使用教程

- C#定时执行BAT脚本:8点、9点与13点任务

- DWR入门教程:快速掌握Ajax整合与开发