使用Chisel生成RISC-V Rocket Chip SoC

"这篇文档是关于RISC-V架构下的Rocket Chip系统级芯片(SoC)生成器的教程,主要介绍了如何使用Chisel语言来构建可配置的SoC生成器。Rocket Chip SoC生成器是一个参数化的SoC生成工具,能够自动生成包含多个核心、缓存系统、内存控制器等组件的复杂SoC设计。"

在当前的计算机体系结构中,RISC-V(精简指令集计算)是一个开放源代码指令集架构,旨在简化硬件设计并提高性能。Rocket Chip SoC Generator是基于RISC-V架构的一种创新方法,它利用了Chisel硬件描述语言的强大功能。Chisel是一种高级的、类型安全的编程语言,允许工程师以更接近于软件编程的方式来设计和实现硬件。

Rocket Chip SoC Generator的主要特点包括:

1. **参数化设计**:可以根据需求定制SoC的配置,如核心数量、是否包含浮点运算单元(FPU)、向量单元以及缓存的大小、关联性和翻译查找表(TLB)条目数等。

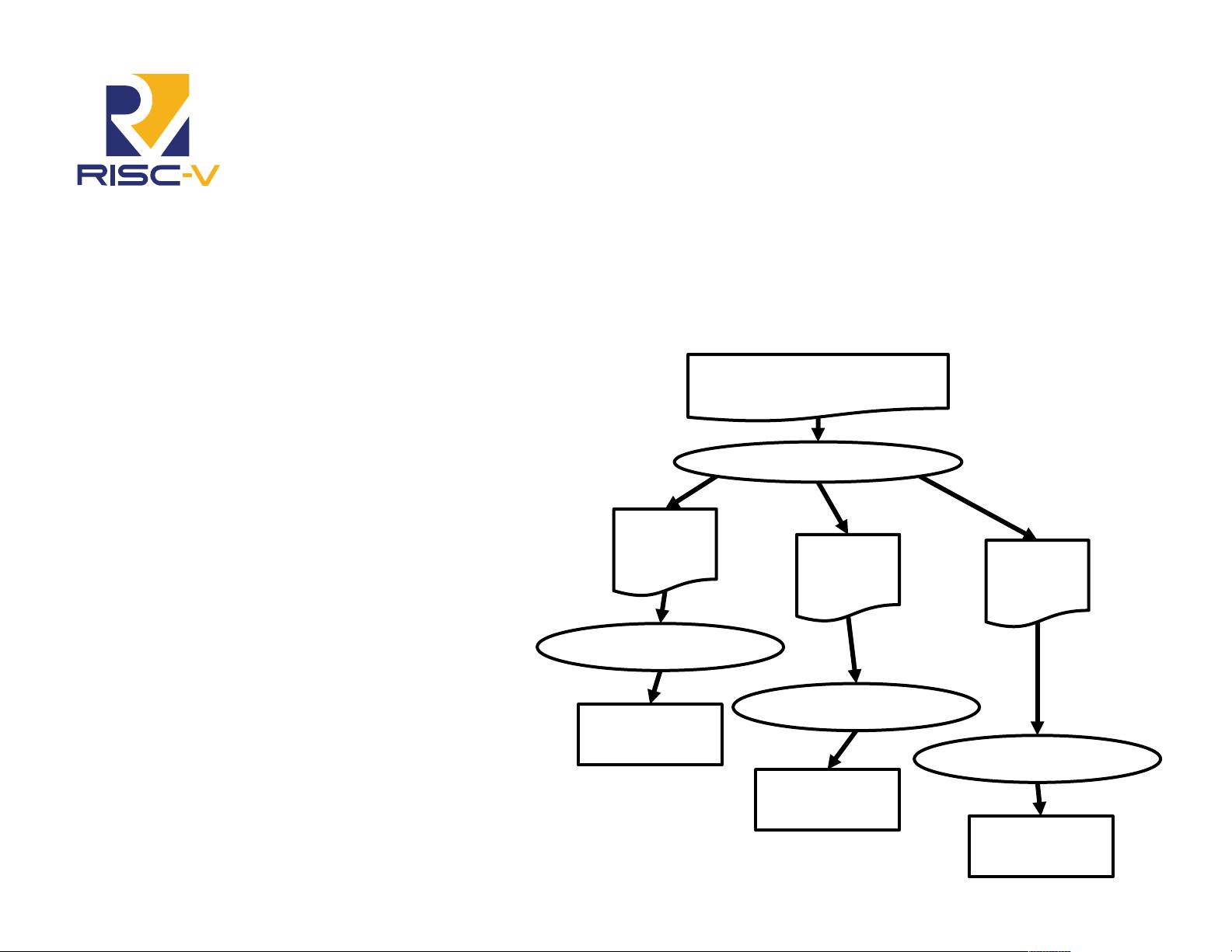

2. **生成Tiles**:每个Tile是一个独立的处理单元,包含Rocket Core(RISC-V处理器核心)及其私有缓存(L1I$和L1D$)。此外,可以添加RoCC(Rocket Custom Coprocessor)加速器以增强特定应用的性能。

3. **生成Uncore组件**:包括一致性代理、共享缓存、DMA引擎(用于内存访问)和内存控制器。这些组件共同构成了SoC的外围内存系统,负责处理多个核心之间的通信和数据交换。

4. **HTIF(Host-Target Interface)生成**:Rocket Chip SoC生成器还生成Host DMA Engine,用于主机与SoC之间的高速数据传输。

5. **L1 Crossbar和Coherence Manager**:这些组件协调不同Tile之间的数据流动,确保缓存一致性。

6. **MemIO接口**:暴露给外部系统的内存接口,允许SoC与其他硬件设备交互。

7. **SoC生成器的优势**:通过这种方式,设计者可以快速探索不同的性能、功耗和面积约束,适应不同的技术节点,以优化芯片设计。这在硬件验证和原型设计阶段尤为重要,因为它大大减少了手动布局和连线的时间。

总而言之,RISC-V Rocket Chip SoC Generator是一个强大的工具,它利用Chisel语言的灵活性,使得系统级芯片的设计变得更加模块化、可配置和可扩展。这种生成器为硬件开发者提供了一种高效的方法,以应对日益增长的计算需求和多变的硬件环境。

467 浏览量

288 浏览量

245 浏览量

2024-10-30 上传

2024-10-31 上传

2024-10-30 上传

336 浏览量

336 浏览量

105 浏览量

shawnbai

- 粉丝: 25

- 资源: 8

最新资源

- 天涯部落版主工具 龙网天涯部落版主工具 v1.2

- rpyc:RPyC(远程Python调用)-用于python的透明和对称RPC库

- shopproject

- 欧美风格主机模板

- doodad:用于 docker、EC2、GCP 等的作业启动库

- 深度学习

- e_commerce-endpoint-rest:电子商务的宁静HATEOAS端点

- STM32 ST-LINK Utility v4.2.0 stlink升级固件.rar

- node-usb:改进的Node.js USB库

- 导出表格,及批量删除.zip

- 行业分类-设备装置-一种抗水防破抗氧化书画纸.zip

- QPD:量子囚徒的困境

- EnumSerialComs:使用 Windows 注册表信息来识别串行 COM 设备-matlab开发

- airmash-frontend:上次官方Airmash应用程序的“半原始”副本

- 服装店收银系统 七彩服装收银系统 v3.2 网络版

- Demo_image-video:托管的演示图像