Xilinx FPGA设计:从RTL级到后仿真的流程解析

需积分: 48 185 浏览量

更新于2024-07-18

2

收藏 790KB DOC 举报

"FPGA后仿真流程"

在FPGA设计中,后仿真是一个至关重要的环节,它确保设计在实际硬件上的行为符合预期。后仿真通常在完成综合和实现过程之后进行,考虑了门级延迟和布局布线的影响,使得仿真结果更加接近实际FPGA的性能。

1. **时序仿真**:

时序仿真关注的是设计中的信号传播时间,它不仅包含了HDL代码在综合后转换成的门级逻辑的延迟,还涵盖了在布局布线阶段引入的连线延迟。这种仿真方式能够帮助设计者评估电路的时序性能,例如能否满足建立时间和保持时间的要求。

2. **综合(Synthesize)**:

综合是将高级语言描述(如VHDL或Verilog)转换为门级逻辑表示的过程。这个阶段生成的仿真模型可以用于后仿真,它包含基本逻辑门和存储元素,如触发器和RAM。

3. **实现(Implement)**:

实现阶段包括翻译、映射和布局布线。翻译和映射处理逻辑优化,而布局布线确定逻辑元素在FPGA芯片上的物理位置并连接它们,这一步会产生实际的时序信息。布局布线后的仿真模型最适合用于时序仿真,因为它考虑了连线延迟。

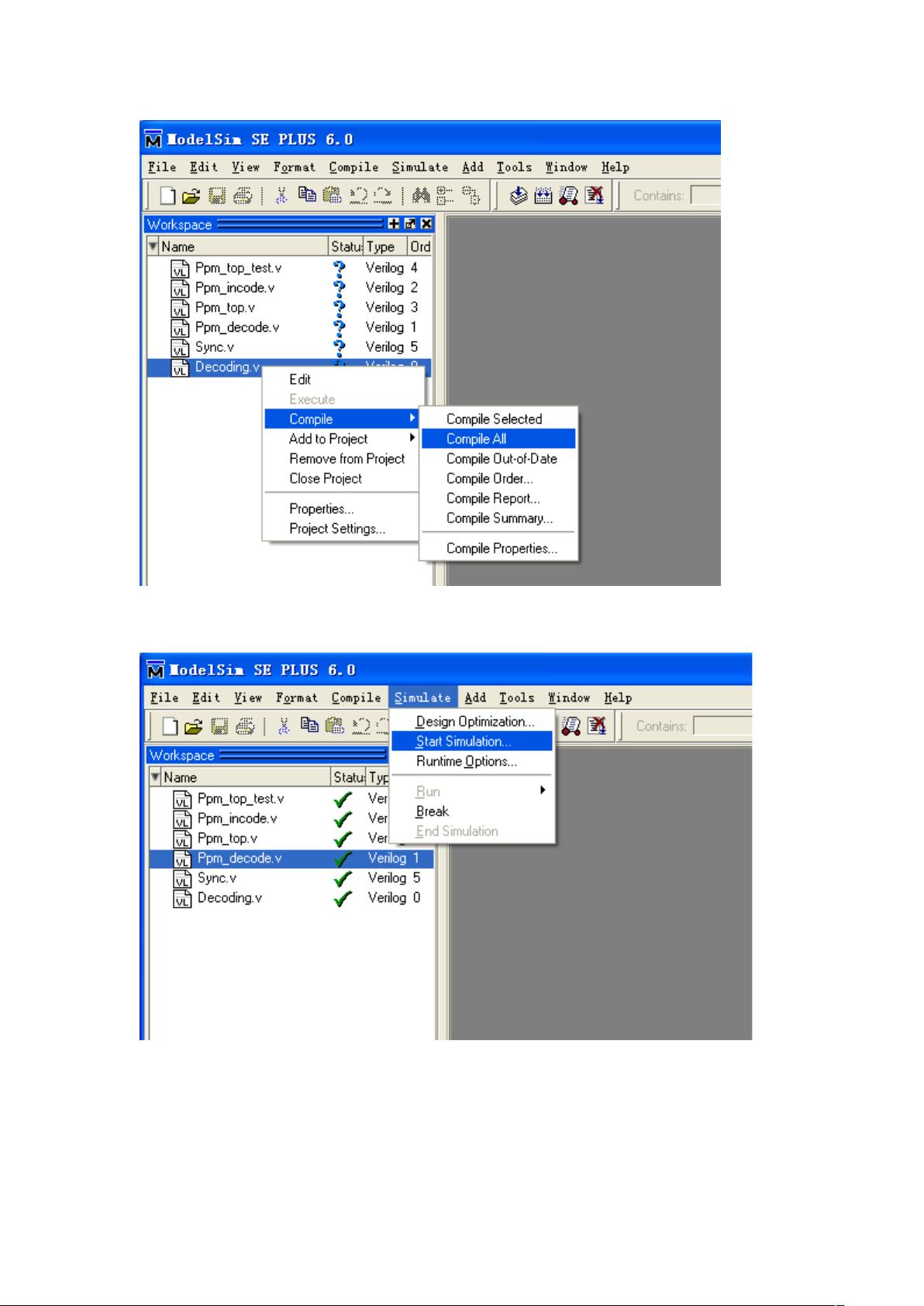

4. **ModelSim仿真**:

ModelSim是一款常用的FPGA仿真工具,用于行为级、RTL级以及后仿真。在RTL级仿真中,设计的逻辑功能被验证;而在后仿真中,除了验证功能外,还会检查时序性能。在ModelSim中,创建新项目、添加源文件、编译、装载文件、设置波形观察以及运行仿真都是必要的步骤。

5. **FPGA开发流程**:

设计通常从行为级开始,然后是RTL级仿真,接着是综合,最后进行后仿真。如果后仿真通过,意味着设计在FPGA上运行的可能性很大。在这个过程中,设计师需要不断地检查和修改设计,直到满足所有时序和功能需求。

6. **ISE ProjectNavigator**:

Xilinx的ISE(Integrated Software Environment)提供了一个集成的开发环境,其中包括项目导航器,用于创建和管理FPGA项目。在后仿真阶段,用户需要在ISE中新建项目,选择合适的器件,并设置综合和实现参数,以便生成用于后仿真的网表文件。

7. **后仿真准备**:

在ISE中完成综合和实现后,生成的网表文件可以导入到ModelSim中进行后仿真。这涉及到选择适当的器件库,设置仿真时钟和其他参数,以确保仿真条件与实际FPGA环境一致。

总结来说,FPGA的后仿真流程是确保设计能够在目标硬件上正确、高效运行的关键步骤。它结合了综合和实现的结果,通过ModelSim等工具进行功能和时序验证,为设计的最终部署提供了信心。

2021-01-19 上传

2011-03-30 上传

2013-04-19 上传

2014-02-23 上传

2021-09-29 上传

2021-01-19 上传

点击了解资源详情