DSP2812 CPU定时器0详解:时钟配置与中断

需积分: 10 172 浏览量

更新于2024-07-29

收藏 326KB DOCX 举报

"该资源详细阐述了TI公司的DSP2812处理器中的CPU定时器0的工作原理和配置,包括时钟倍频、分频、定时器结构及其与系统时钟的关系。"

在嵌入式系统中,定时器是至关重要的组成部分,用于执行各种时间相关的任务,如中断服务、脉冲产生、延时计算等。TI的TMS320F28x系列DSP芯片中的CPU定时器0是32位定时器,具备高度的灵活性和可配置性。本资源主要关注定时器0的使用,它与其他两个CPU定时器1和2略有不同,后两者通常被预留用于DSPBIOS或RTOS。

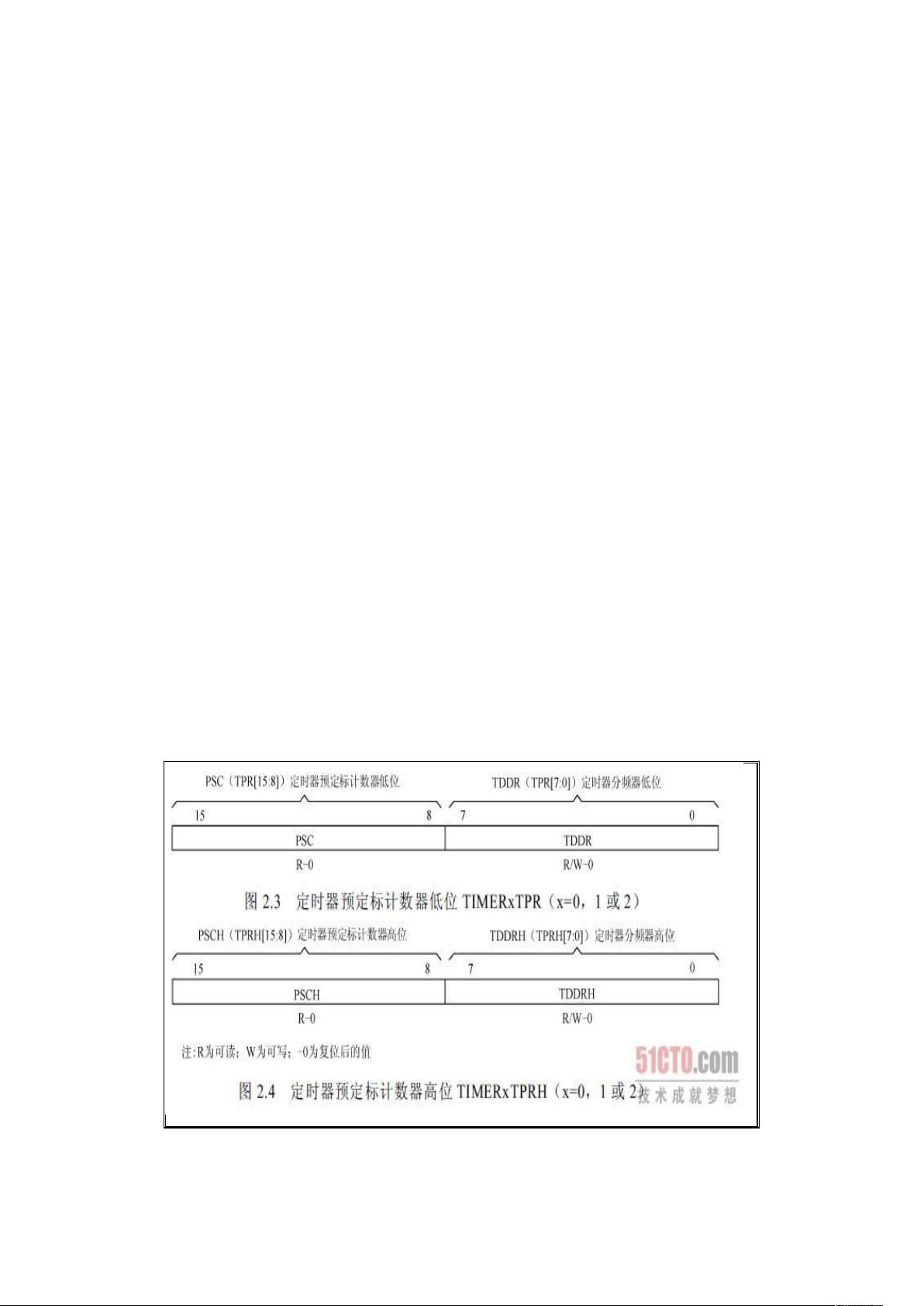

定时器的基本结构包括预定标计数器(PSCH:PSC)和计数器(TIMH:TIM)。定时器0的时钟源可由系统时钟SYSCLKOUT提供,其时钟频率可以通过倍频和分频进行调整。当TSS(TIMERxTCR[4])设置为0时,定时器使用未经倍频的系统时钟。分频器(TDDRH:TDDR)预先设定一个分频值,每个系统时钟周期结束后,预定标计数器会减一,直到减到0,此时会产生一个新的定时器周期,也就是定时器时钟。定时器时钟频率等于系统时钟频率除以分频值。

系统时钟SYSCLKOUT的频率受到锁相环(PLL)的控制,其工作状态和频率由PLLCR[3:0](即DIV)决定。如果在上电复位期间GPIOF14引脚保持高电平,PLL会被启用。当PLL启用并且DIV不为0时,系统时钟会被倍频,其频率范围取决于外部晶振的频率和DIV的值。如果DIV=10,外部晶振最大可以是30MHz,从而产生150MHz的SYSCLKOUT。

定时器的计数器(TIMH:TIM)在每个定时器周期内减一,当减到0时,会重新加载预设的周期值(PRDH:PRD)并触发TINT中断。这种工作模式使得定时器可以用来实现周期性的任务或者精确的时间间隔测量。

总结来说,DSP2812的CPU定时器0是一个功能强大的定时器,它的时钟源可以灵活配置,既可以使用未经倍频的系统时钟,也可以通过锁相环进行倍频。通过适当的分频和计数器设置,可以实现各种定时需求,并通过中断机制与处理器核心交互,执行相应的程序逻辑。理解这些知识点对于开发基于TI DSP的嵌入式系统至关重要。

1071 浏览量

205 浏览量

113 浏览量

2009-08-19 上传

121 浏览量

265 浏览量

430 浏览量

184 浏览量

105 浏览量

zjlhongye

- 粉丝: 0

- 资源: 2

最新资源

- torch_cluster-1.5.6-cp38-cp38-win_amd64whl.zip

- librtmp zlib openssl源码 编译方法 编译工具 编译好的librtmp.lib合集.zip

- gimp-plugin-helloworld:GIMP插件Hello World示例

- doncidomper

- matlab的slam代码-LIR-SLAM:基于MATLAB的SLAM

- 统一配置文件操作接口INI_XML_JSON_DB_ENDB

- sanic-dispatcher:Sanic的Dispatcher扩展,还可以用作Sanic到WSGI的适配器

- 歌词

- torch_sparse-0.6.5-cp36-cp36m-linux_x86_64whl.zip

- hello:你好科尔多瓦

- redis-5.0.8.zip

- pretweetify-crx插件

- 人力资源管理企业文化PPT

- my-repo-from-remote:此存储库是从Github创建的

- slackhook:轻松将Slack Webhook集成添加到您的Ruby应用程序

- 温湿度控制电路图.rar