嵌入式ARM多核处理器并行化优化技术探析

17 浏览量

更新于2024-08-31

收藏 259KB PDF 举报

"本文主要探讨了在单片机与DSP中的嵌入式ARM多核处理器如何实现并行化方法,以提升系统性能。由于嵌入式多核处理器的广泛使用,但其软件开发技术尚未充分利用多核优势,文章着重于任务并行和缓存优化两个方面的研究,旨在为嵌入式平台上的程序并行化提供优化策略。文章以同构结构的嵌入式多核处理器,如ARM的SMP处理器为例进行分析,以OMAP4430双核处理器为具体研究对象,解析其处理器结构和缓存机制,以期找到适应嵌入式环境的并行化优化方案。"

在当前的嵌入式系统中,多核处理器的应用已经成为主流,然而,相应的软件开发技术并未跟上硬件发展的步伐,传统的单核编程模式限制了多核处理器性能的发挥。程序并行化优化虽然在PC平台上已有一定的实践,但在嵌入式领域却相对滞后,这主要是因为嵌入式多核处理器与PC平台的多核处理器在架构和使用场景上存在显著差异。

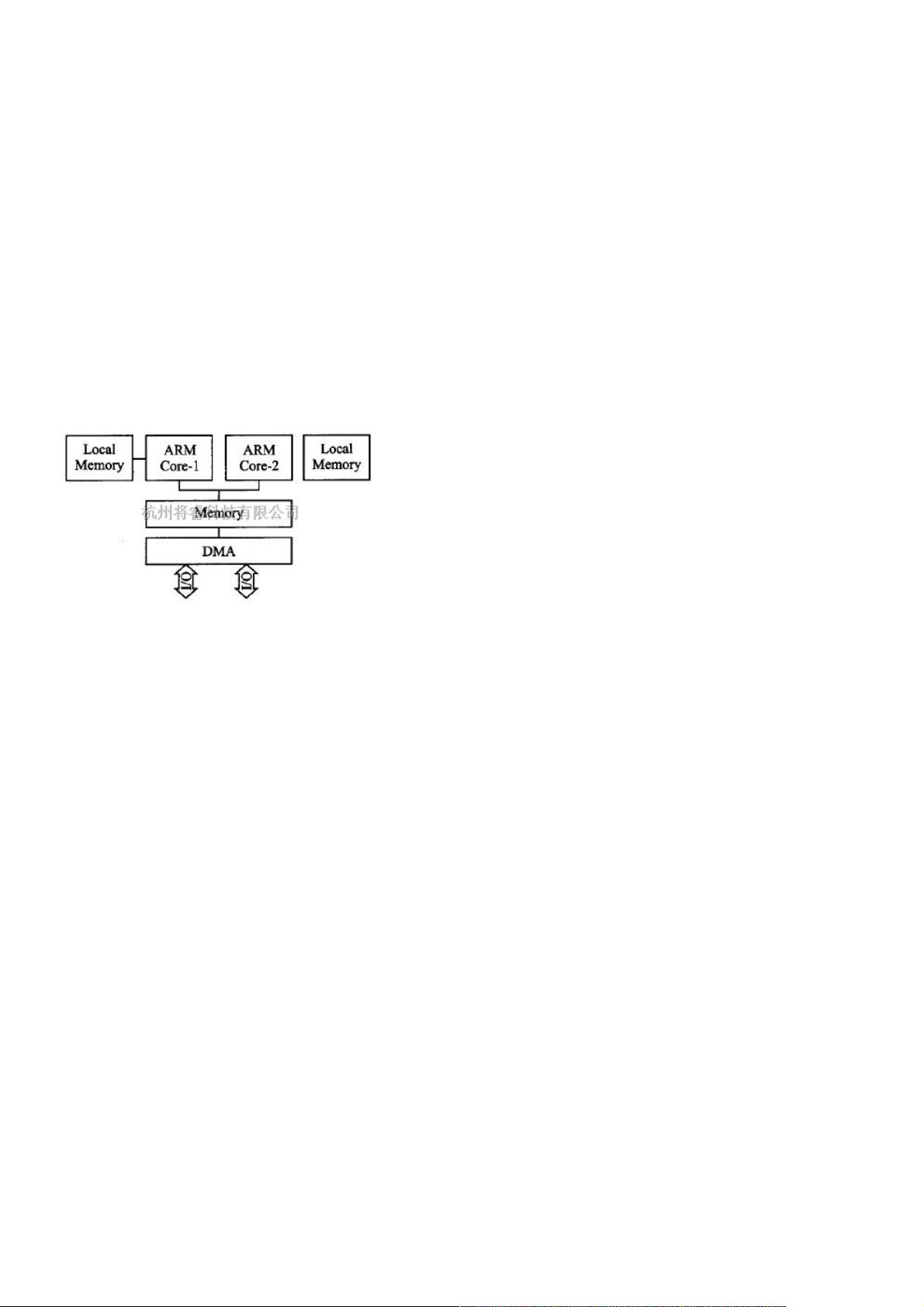

嵌入式多核处理器分为同构和异构两种类型。同构处理器所有核心拥有相同的架构,常见于PC多核处理器中,允许相同代码在不同核心上并行运行。而异构处理器则由不同类型的核组成,如通用CPU核与DSP核的组合,适用于嵌入式系统的复杂计算需求。本文重点研究的同构结构,如ARM的SMP(对称多处理)架构,其特点是所有处理器具有相同的硬件配置,共享公共资源,每个处理器都有自己的私有内存(L1 Cache)以及共享的二级缓存(L2 Cache)以处理多核间的通信。

以OMAP4430为例,它是一个典型的ARM SMP处理器,其双核设计使得并行化处理成为可能。每个核心都拥有独立的L1 Cache,以支持高速数据访问,同时通过L2 Cache协调多个核心间的数据交换,确保高效协作。在这样的环境下,任务并行化是通过将任务分解,分配给不同的核心执行,以提高执行效率。而缓存优化则是通过合理利用缓存层次结构,减少数据在主存与缓存之间的频繁交互,降低访问延迟,提高整体系统性能。

为了实现并行化优化,首先需要进行任务分解,将可并行化的部分划分出来,避免数据依赖,使得各任务可以独立运行。此外,还需要考虑负载均衡,确保每个核心的工作量大致相等,避免某些核心过载而其他核心闲置。同时,对缓存的优化涉及数据局部性原则,尽量使数据在访问时保持在缓存中,减少缓存失效带来的性能损失。这可能需要程序员在编写代码时考虑到数据访问模式,或者通过编译器的自动并行化工具辅助优化。

针对嵌入式多核处理器的并行化方法,需要结合任务并行和缓存优化两个关键点进行深入研究。在理解和掌握了处理器的结构特点后,可以设计出更适合嵌入式环境的并行算法,以充分利用多核处理器的潜力,提高系统运行速度和响应能力,从而满足日益增长的计算需求。

2008-12-03 上传

2020-07-23 上传

2020-08-09 上传

2020-08-06 上传

2012-08-29 上传

2021-09-06 上传

2021-11-19 上传

点击了解资源详情

点击了解资源详情

weixin_38685608

- 粉丝: 1

- 资源: 995

最新资源

- demi-cluster:demi.ro的代码

- 使用 Matlab 进行特征选择:选择使正确分类率最大化的特征子集。-matlab开发

- SpringMVC_Project

- Profile.Api

- 缓存搜索框的搜索记录

- Link_start:任务中使用的链接:fire:

- angular-price-io

- Accuinsight-0.0.186-py2.py3-none-any.whl.zip

- Memories-App:一个简单的社交媒体 MERN 应用程序,允许用户发布他们生活中发生的有趣事件

- Smart-Parking-System---MATLAB

- UOL-crx插件

- ZenTimings

- 基于PHP的最新小储云商城免授权PHP源码.zip

- 模拟量4-20ma转换程序.rar

- Accuinsight-1.0.29-py2.py3-none-any.whl.zip

- Cloud_Ramos