西南交大数电实验报告:Verilog组合逻辑电路设计与仿真

版权申诉

25 浏览量

更新于2024-02-27

收藏 2.35MB DOCX 举报

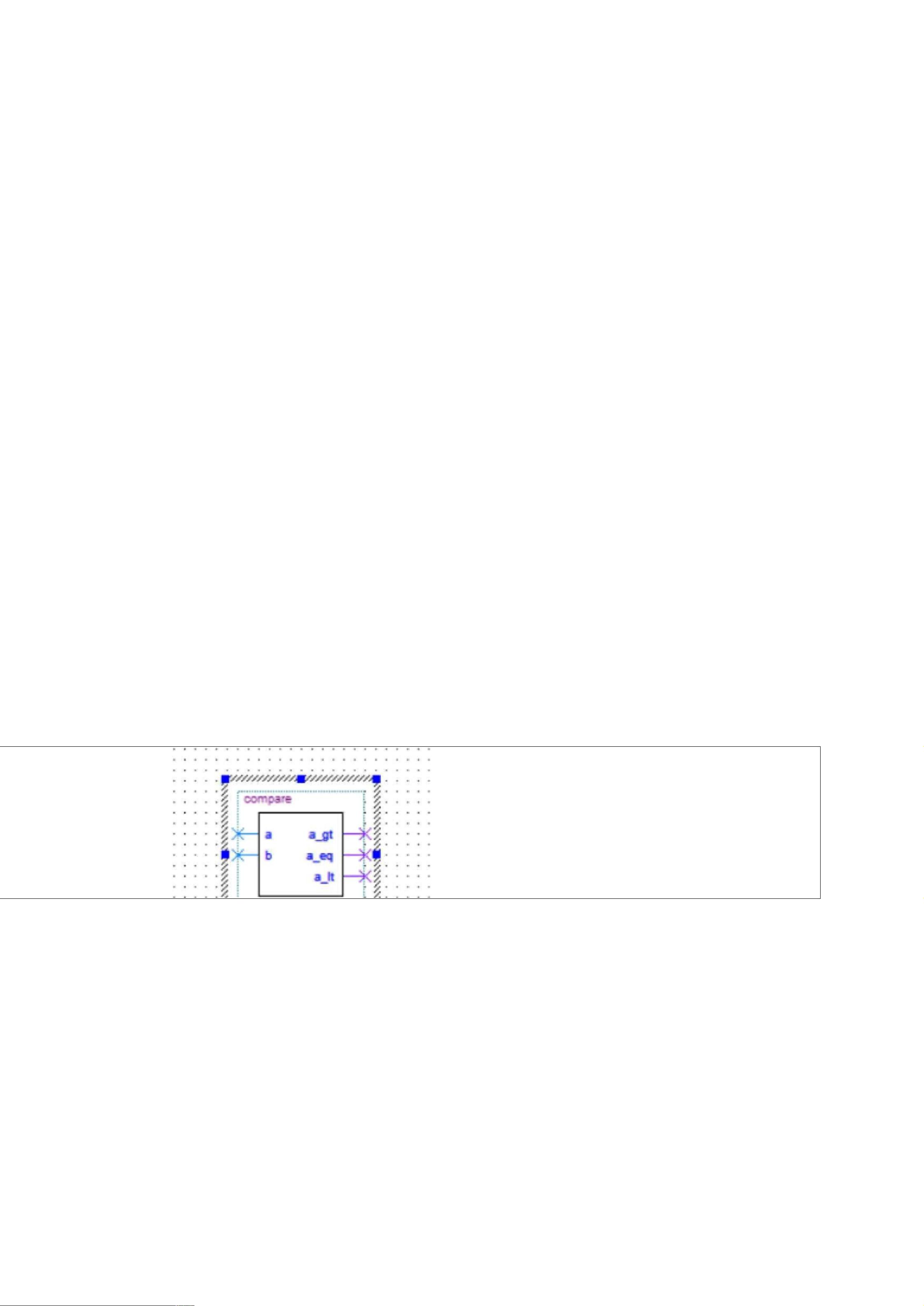

_lt == 1'b0 && a_eq == 1'b0 && a[a[a_lt == 1'b0 && a_eq == 1'b1 && a_gt == 1'b0;endmodule1.2 仿真结果WaveDrom代码:```{ "signal": [ { "name": "a", "wave": "01....", "data": "1001101010" }, { "name": "b", "wave": "3.", "data": "1010101011" }, { "name": "LT", "wave": "01.0", "data": "1001000100" }, { "name": "EQ", "wave": "0.10", "data": "0100100010" }, { "name": "GT", "wave": "0.1.", "data": "0010010001" } ]}```1.3 实验分析在本实验中,我们设计了一个一位数值比较器,该比较器可以比较两个1位数的大小,输出结果包括大于、等于和小于。通过Verilog代码的编写和仿真波形的验证,我们验证了比较器的正确性和准确性。2. Verilog描述组合逻辑电路描2.1 源代码module logic_gate(x,y,and_out,or_out,xor_out);input x,y;output and_out,or_out,xor_out;assign and_out = x && y;assign or_out = x || y;assign xor_out = x ^ y;endmodule2.2 仿真结果WaveDrom代码:```{ "signal": [ { "name": "x", "wave": "01....", "data": "1001101010" }, { "name": "y", "wave": "3.", "data": "1010101011" }, { "name": "AND_OUT", "wave": "010.", "data": "1000100001" }, { "name": "OR_OUT", "wave": "0..1", "data": "0011101111" }, { "name": "XOR_OUT", "wave": ".1", "data": "1011001010" } ]}```2.3 实验分析在本实验中,我们设计了一个逻辑门电路,该电路包括与门、或门和异或门。通过Verilog代码的编写和仿真波形的验证,我们验证了逻辑门电路的正常运行和输出结果的正确性。3. Quartus II软件的使用在本实验中,我们使用了Quartus II软件进行原理图设计和逻辑仿真。通过熟练使用Quartus II软件,我们能够高效地设计和仿真数字电路,提高了实验的效率和准确性。通过本实验的学习,我们对数字电路的原理和设计有了更加深入和全面的理解。4. 实验总结通过本次数电实验,我们学习了Verilog语言的编写和逻辑电路设计的基本原理。在实验中,我们通过具体的比较器和逻辑门电路的设计,加深了对数字电路的理解和应用。通过Quartus II软件的使用,我们掌握了数字电路的原理图设计和仿真方法。通过实验的学习和总结,我们对数字电路的理论知识和实践操作有了更深入的认识,为今后的学习和研究打下了坚实的基础。通过本次实验,我们不仅掌握了数字电路的基本原理和方法,也提升了解决问题和实践应用的能力,为今后的学业和工作打下了坚实的基础。通过本次实验的学习和实践,我们对数字电路的原理和设计有了更加深入和全面的理解,为今后的学习和研究打下了坚实的基础。

2022-07-14 上传

2022-07-14 上传

2022-07-14 上传

2022-07-06 上传

2022-05-23 上传

2022-05-23 上传

点击了解资源详情

不吃鸳鸯锅

- 粉丝: 8524

- 资源: 2万+

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍