VHDL实现的FPGA有限状态机设计与优势分析

需积分: 25 71 浏览量

更新于2024-08-02

收藏 226KB PDF 举报

"这篇资料主要介绍了在FPGA设计中如何使用有限状态机(FSM),适合初学者作为设计参考。"

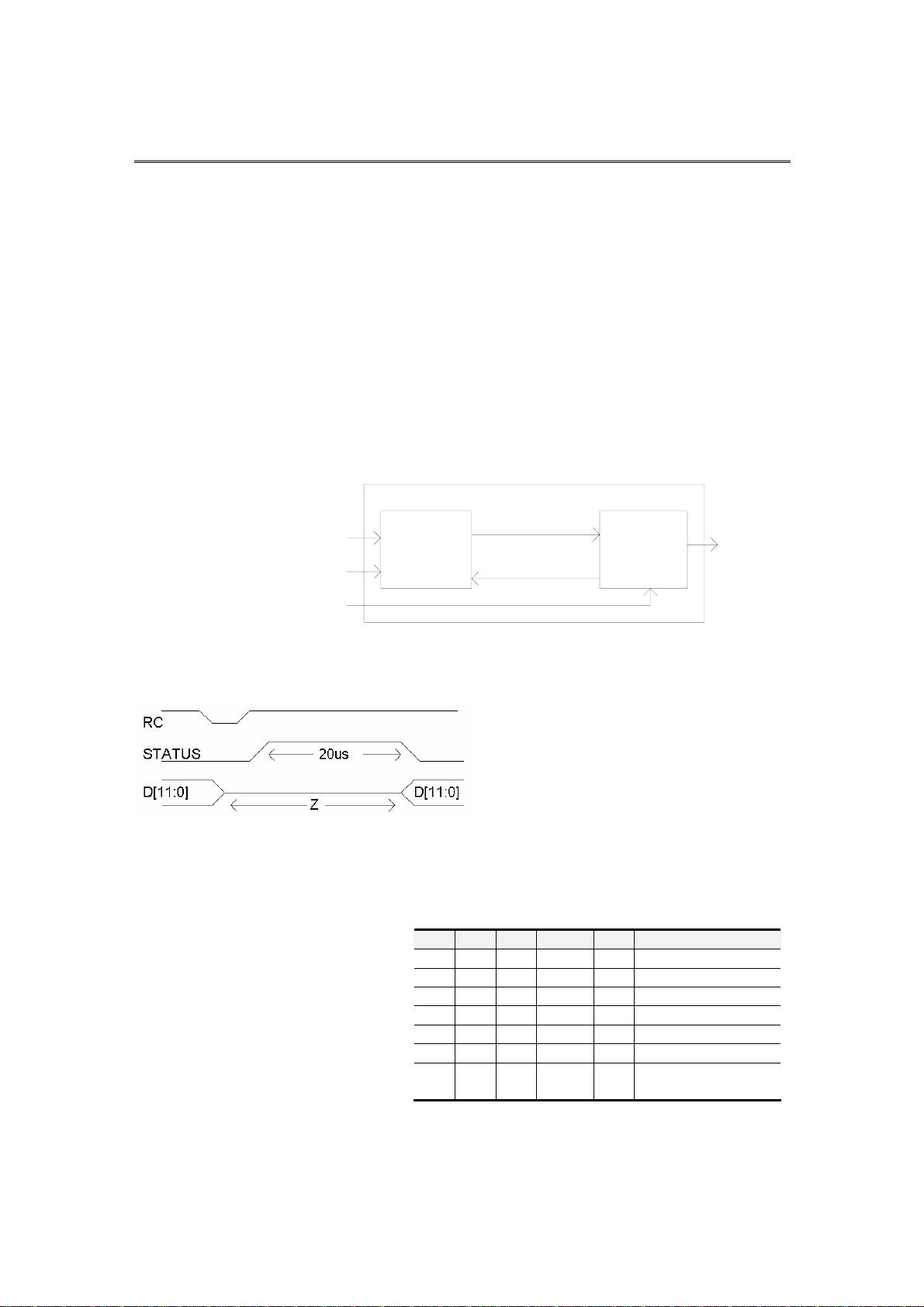

在FPGA设计中,有限状态机(Finite State Machine, FSM)是一种常用的数字逻辑设计方法,它能有效地描述和实现各种逻辑系统。FSM在VHDL中的应用广泛,具有诸多优点:

1. **简洁性与优化**:FSM的结构清晰,通常采用枚举类型的符号状态,使得设计方案易于理解和实现。VHDL综合器能够充分利用这种结构进行优化,提高设计效率。

2. **同步时序逻辑**:FSM是构建高性能同步时序逻辑模块的理想选择,能够有效解决大规模逻辑电路设计中的竞争冒险问题。综合器针对FSM的优化功能进一步增强了这一优势。

3. **可读性和维护性**:VHDL中的FSM设计层次分明,代码结构清晰,便于调试、修改和复用。对于初学者来说,学习和掌握FSM的设计技巧相对容易。

4. **高速运算与控制**:一个FSM可以由多个进程构成,甚至一个设计实体内可以包含多个并行运行的FSM,这与多CPU系统类似。它们能在单个时钟周期内完成多个操作,运行速度远超按指令执行的CPU。

5. **高效率**:与CPU执行指令相比,状态机的转换仅需一个时钟周期,而且可以同时进行多个运算和控制操作。因此,FSM在处理复杂控制逻辑时,其速度可能比CPU快两个数量级。

6. **可靠性**:FSM在硬件中的实现比CPU执行软件更可靠,因为硬件错误率通常低于软件错误,尤其是对于要求高容错性的系统,使用FSM可以提供更好的故障防护。

7. **广泛应用**:状态机在通信、工业控制、军事和其他领域有广泛的应用,尤其是在需要高速运算和精确控制的场合,FSM通常是首选方案。

通过深入学习和实践,开发者能够利用FSM的强大功能,设计出高效、可靠的FPGA系统。对于初学者来说,理解FSM的基本原理,掌握VHDL中描述和实现FSM的方法,将对提升FPGA设计能力大有裨益。

114 浏览量

162 浏览量

2023-08-31 上传

216 浏览量

243 浏览量

2024-04-19 上传

2020-10-17 上传

2021-07-13 上传

275 浏览量

hubwh

- 粉丝: 0

最新资源

- OpenGL实现旋转的glut代码教程

- Diagramos:一元逻辑公式证明工具的应用介绍

- Spring Security 2.0.4 完整包及源码下载

- 雪球用户数据爬取及多维数据集导入教程

- MARC2015实例教程第5-6-9章节及常见问题解析

- Qt与Matlab混合编程实现加法教程及文件下载

- PHP分页类实现数据库操作教程

- 基于MSP430F149实现的12864显示屏简便串口通信

- HashUtil:简易校验和哈希计算器工具使用指南

- PHPUnit代码测试库dbunit下载与应用

- C#实现调用本机摄像头及截图操作

- 高中生Santhosh探索自动化、AI与TensorFlow学习之路

- C#实现24路舵机控制板编程及USB通信

- 银行家算法在vc++环境下的实现教程

- 探索 Maven Findbugs 插件在 Java 开发中的应用

- RecruitHerd Mini-crx插件: 招聘软件解决方案的简化版