CPSK调制解调系统实现与仿真分析

需积分: 9 148 浏览量

更新于2024-09-09

收藏 95KB DOC 举报

"CPSK调制与解调系统的设计"

本文主要介绍了一种CPSK(Coherent Phase Shift Keying)调制解调系统的设计,包括其基本原理、设计要求、方框图以及VHDL程序实现。CPSK是一种利用载波相位变化来传递数字信息的调制技术,特别适用于无线通信系统。

CPSK调制是通过改变载波相位来传输数据。在二进制2CPSK中,通常设置相位π代表“0”码,相位0代表“1”码。这意味着当数字基带信号为“0”时,已调制信号相对于载波的相位偏移为π;而当数字基带信号为“1”时,相位保持为0,即与载波同相。这种调制方式可以表示为数学公式,其中[pic]表示载波的初始相位,载波相位仅在0和π之间变化。

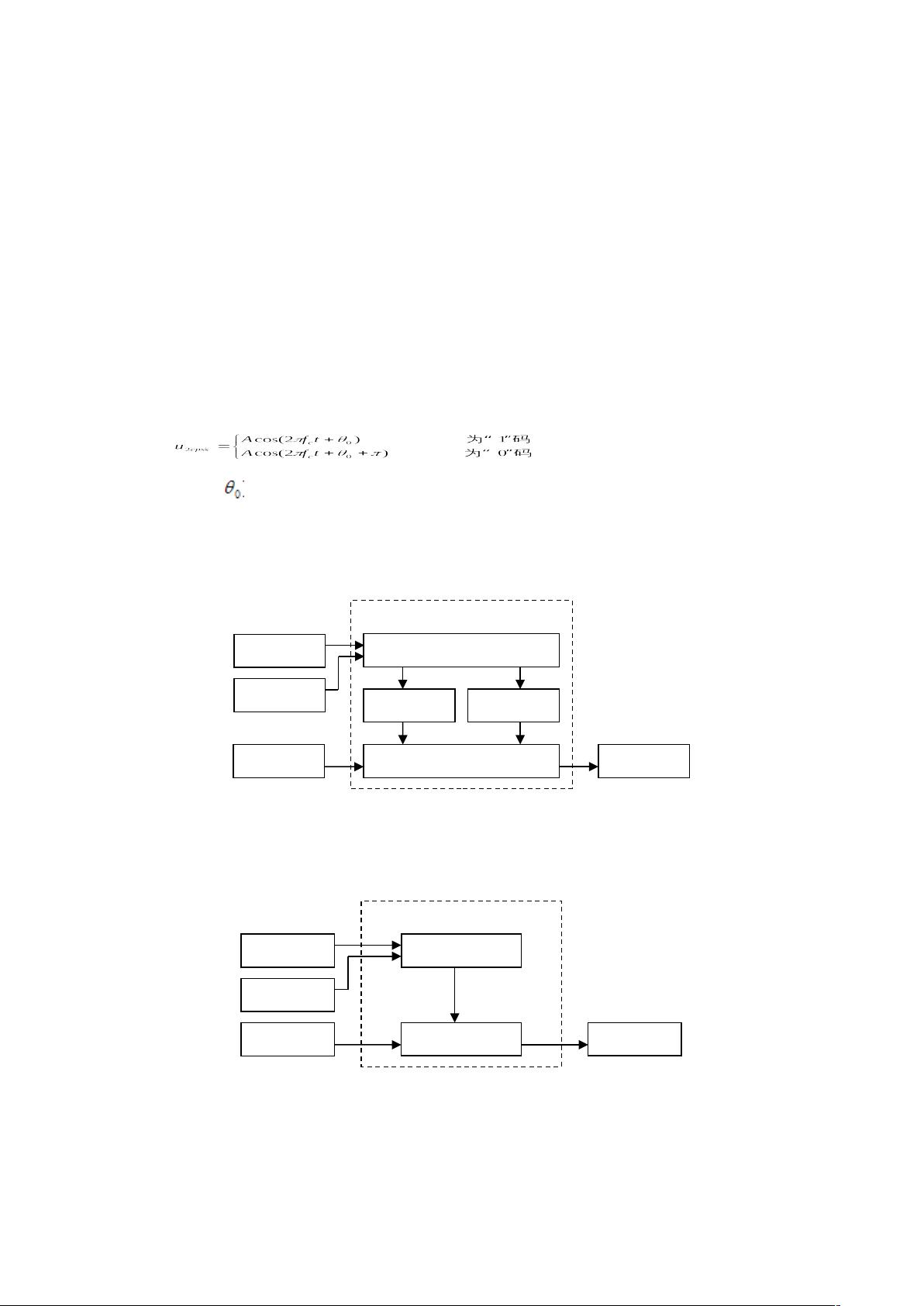

设计CPSK调制解调器时,调制方框图通常包括载波生成、相位选择和信号混合等步骤。解调方框图则涉及相位比较和恢复原始数字基带信号的过程。在VHDL编程中,通常会使用计数器生成两个相位相差90度的载波信号,根据基带输入信号选择相应的相位输出,以此实现调制。例如,当基带信号为‘1’时,输出信号为与第一相位信号(f1)一致,而当基带信号为‘0’时,输出信号与第二相位信号(f2)一致。为了能够观察载波信号,可以将f1信号引出并记录为f3。

在实际的VHDL程序设计中,输入包括系统时钟(clk)、启动信号(start)、基带信号(x),输出为已调制信号(y)和辅助观察信号f3。通过一个2位计数器来切换相位,确保在时钟上升沿触发相位更新,并根据start信号重置计数器。计数器的值决定了输出是f1还是f2,从而实现CPSK调制。

CPSK调制解调系统的仿真分析对于理解信号传输性能、误码率和抗干扰能力等方面至关重要。通过VHDL实现,可以进行硬件级别的模拟,验证设计的正确性和效率。此外,CPSK系统在实际应用中还需要考虑信道特性、噪声影响以及同步等问题,以确保可靠的数据传输。

2023-06-06 上传

点击了解资源详情

点击了解资源详情

2022-09-23 上传

点击了解资源详情

点击了解资源详情

2010-08-10 上传

2021-10-01 上传

2021-10-12 上传