74HC595详解:8位串行输入并行输出移位寄存器

"这篇资料是关于74HC595集成电路的使用方法,详细介绍了该芯片的特性、规格以及应用场景。"

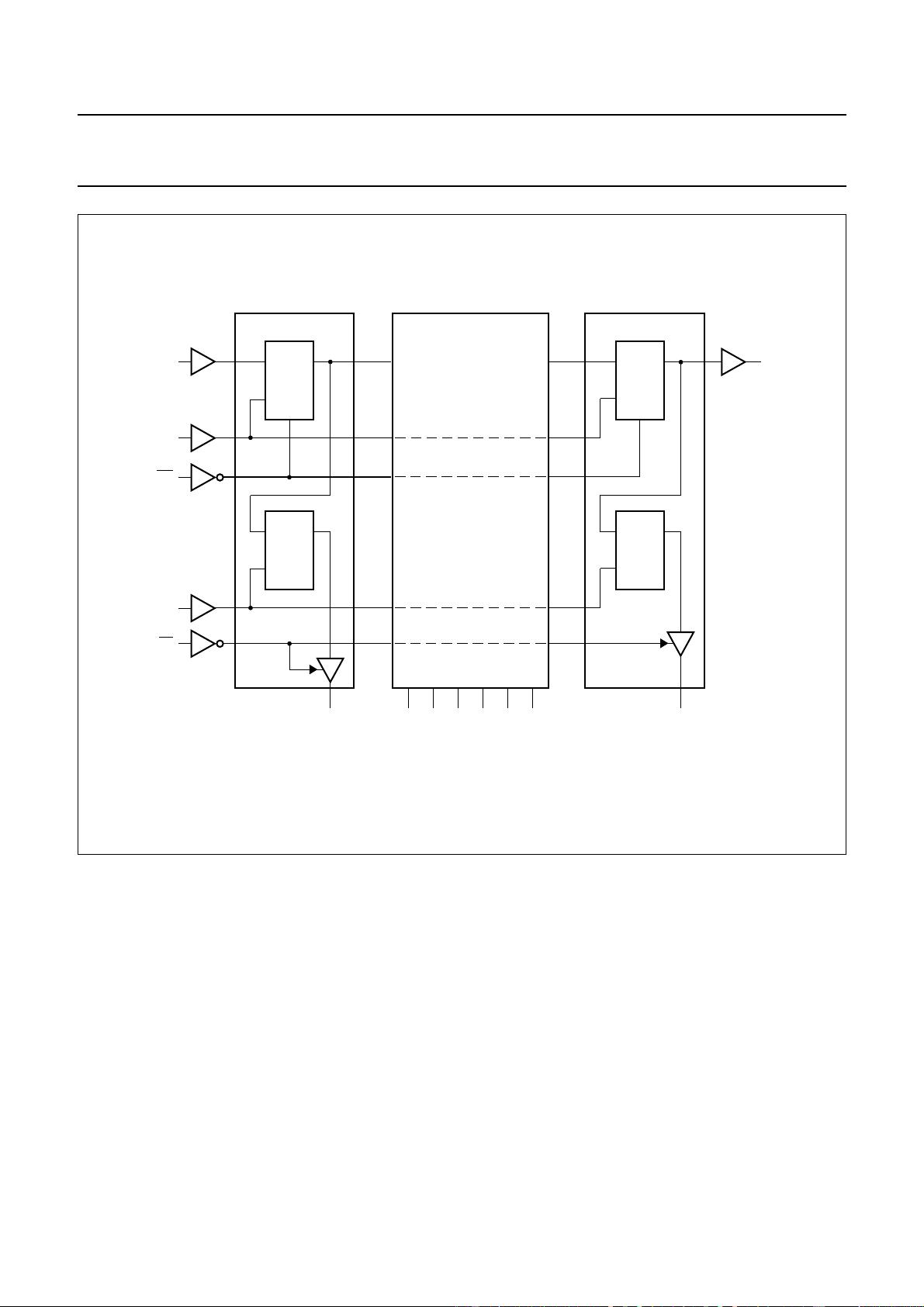

74HC595是一款8位串行输入、串行或并行输出的移位寄存器,带有3态输出锁存器。它在高速硅门CMOS技术下制造,与低功耗肖特基TTL(LSTTL)引脚兼容,并符合JEDEC标准7A。这款芯片的特点和功能包括:

1. **8位串行输入**:数据通过串行方式输入到寄存器中,适合处理多位数据传输。

2. **8位串行或并行输出**:数据不仅可以串行输出,也可以并行输出,提供了灵活的数据读取方式。

3. **存储寄存器与3态输出**:存储寄存器用于存储数据,3态输出意味着输出端口可以根据需要被使能或禁用,从而节省电源和提高系统设计的灵活性。

4. **独立的移位时钟和存储时钟**:移位寄存器和存储寄存器拥有各自的时钟输入,这允许它们在不同的时序下工作,增加了设计的复杂性和灵活性。

5. **高移位频率**:可以达到100MHz的典型移位输出频率,适用于需要快速数据处理的应用。

6. **ESD保护**:具有超过2000V的Human Body Model (HBMEIA/JESD22-A114-A) 和超过200V的Machine Model (MMEIA/JESD22-A115-A) 的静电放电保护,提高了芯片在使用过程中的可靠性。

74HC595常用于以下应用场合:

- **串行到并行数据转换**:它可以将串行输入的数据转化为并行输出,适合在需要快速访问多个数据线的系统中。

- **远程控制的保持寄存器**:在远程控制系统中,74HC595可以用来存储和暂时保持控制信号,直到被后续电路处理。

在实际使用中,SH_CP输入端口的正沿触发数据移位,而ST_CP(存储时钟)输入用于控制数据从移位寄存器转移到存储寄存器。还有一个名为DS(数据输入)的引脚用于输入数据,而Q0至Q7则是8位并行输出端口。另外,有一个SER(串行输入)引脚用于连续输入数据,而一个RST(清除)引脚用于清零整个寄存器。

了解这些基本信息后,设计者可以结合74HC595的特性,根据具体项目需求,如数据速率、接口兼容性等,将其集成到各种数字逻辑电路中,实现高效的数据处理和传输。

944 浏览量

393 浏览量

225 浏览量

2013-05-01 上传

2022-07-14 上传

点击了解资源详情

208 浏览量

wy191268906

- 粉丝: 0

最新资源

- RxCombine实现RxSwift与Apple Combine双向桥接

- 白血病图像分类模型与数据集发布

- 快J-crx插件:提高看J图效率的扩展程序

- CSS技术在美食页面设计中的应用

- 掌握Swift:以任意方式编写高效HTML指南

- 深入解析CSS、QSS与Less技术及Qt框架应用

- NavalPlan: ZK框架下项目管理软件的源代码解析

- 教堂信仰CSS网页模板 - 旅游景点设计与下载

- 深入探索Java7源码:Turing Machine实战案例解析

- 海尔企业文化的创新实战模式

- Ekran Avcısı:一站式屏幕截图与分享Chrome扩展

- 拼字游戏Scrabble推荐系统实现与优化

- 探索食品订购网站背后的HTML技术

- 营销管理宝典:卓越广告大师参考指南

- React开发必备:react-sticky粘性库使用详解

- Java实战项目:推箱子游戏源码解读与使用