VHDL驱动的8位模型计算机设计与实现

下载需积分: 50 | DOC格式 | 638KB |

更新于2024-07-19

| 175 浏览量 | 举报

本文主要探讨的是VHDL( VHDL,一种硬件描述语言)在模型机设计中的应用,特别是针对8位模型计算机的构建。随着信息技术的飞速发展,计算机已成为日常生活中不可或缺的一部分,其性能提升的需求推动了相关研究的深入。然而,理解计算机内部复杂的电路和逻辑结构对于学习者和开发者来说是一项挑战。为此,作者利用VHDL,这是一种用于描述数字逻辑系统和集成电路设计的高级编程语言,设计了一个直观易懂的8位模型计算机。

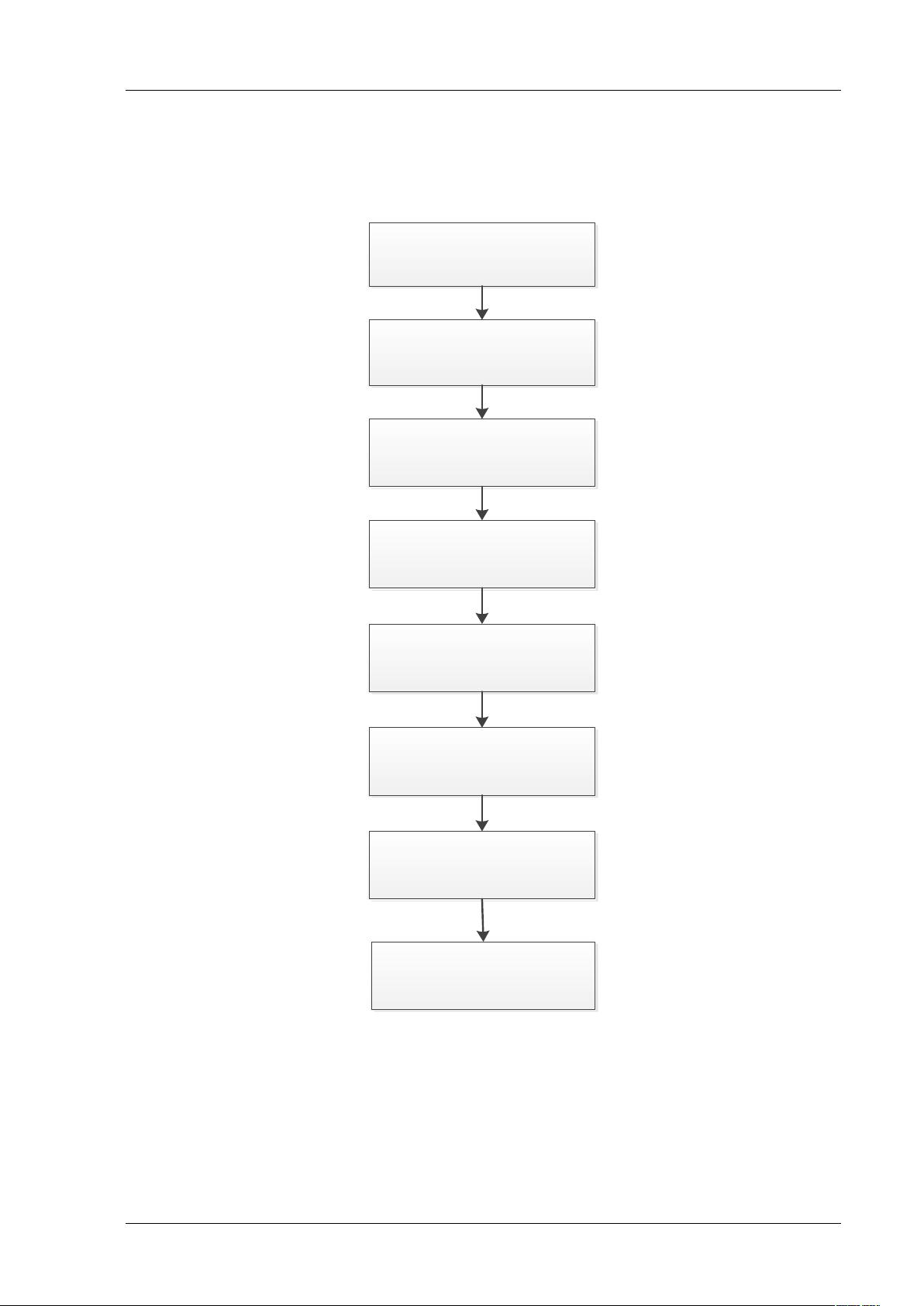

文章首先概述了8位模型计算机的基本原理,它是一种简化版的计算机架构,旨在模拟真实计算机的核心组件,如算术逻辑运算单元(ALU)、累加器、控制器、地址寄存器、程序计数器(PC)、数据寄存器、存储器、节拍发生器、时钟信号源、指令寄存器和指令译码器等。这些模块的精心设计使得研究人员能够更好地理解计算机内部运作机制。

接下来,作者详细介绍了各个模块的功能和设计过程。例如,算术逻辑运算单元负责执行基本的算术和逻辑操作,累加器则用于暂存运算结果,控制器控制各个部件之间的通信,而地址寄存器则存储内存地址。其他如程序计数器用于跟踪指令执行流程,数据寄存器则用于存储中间数据,存储器则作为数据的临时存放地。

在设计过程中,作者选择使用Quartus II 9.0这款流行的硬件设计工具,它支持VHDL编程,使得整个设计过程更为高效。通过这个平台,作者能够将VHDL代码转化为实际的硬件电路,从而验证模型机的逻辑功能和性能。

整个项目的实现不仅体现了VHDL在数字控制系统设计中的强大实用价值,还为学习者提供了一种实践计算机体系结构的好方法。通过这个8位模型机,读者可以更加直观地理解计算机的工作原理,包括指令执行流程、数据处理以及硬件层面的控制逻辑。

本文是一篇结合计算机组成原理和数字逻辑设计的实践性论文,通过构建8位VHDL模型机,展示了如何利用VHDL语言进行系统级的设计,并通过Quartus II软件平台进行实际的硬件实现,这对于深入理解计算机内部构造和优化数字系统设计具有重要的参考价值。

相关推荐

「已注销」

- 粉丝: 1

最新资源

- C#实现程序A的监控启动机制

- Delphi与C#交互加密解密技术实现与源码分析

- 高效财务发票管理软件

- VC6.0编程实现删除磁盘空白文件夹工具

- w5x00-master.zip压缩包解析:W5200/W5500系列Linux驱动程序

- 数字通信经典教材第五版及其答案分享

- Extjs多表头设计与实现技巧

- VBA压缩包子技术未来展望

- 精选多类型导航菜单,总有您钟爱的一款

- 局域网聊天新途径:Android平台UDP技术实现

- 深入浅出神经网络模式识别与实践教程

- Junit测试实例分享:纯Java与SSH框架案例

- jquery xslider插件实现图片的流畅自动及按钮控制滚动

- MVC架构下的图书馆管理系统开发指南

- 里昂理工学院RecruteSup项目:第5年实践与Java技术整合

- iOS 13.2真机调试包使用指南及安装