VHDL设计进阶:信号与变量赋值,电路实例解析

版权申诉

PPT格式 | 1.09MB |

更新于2024-07-03

| 3 浏览量 | 举报

"可编程逻辑器件(EDA):第5章 VHDL设计进阶.ppt"

在电子设计自动化(EDA)领域,VHDL是一种广泛使用的硬件描述语言,用于设计和验证数字系统的逻辑行为。本章重点讲解了VHDL设计的进阶技巧,通过深入理解数据对象、设计实例及语法内涵,提升VHDL设计能力。

首先,VHDL中的数据对象是设计的基础,主要包括常数、变量和信号。常数是不可改变的值,在设计中用作固定参数,确保设计过程中某特定值的稳定性。变量则在程序中存储瞬时变化的数据,其赋值操作是立即完成的。而信号则模拟实际硬件中的连接,它们的变化可能会异步传播,因此信号赋值通常发生在进程之外,并可能有延迟。

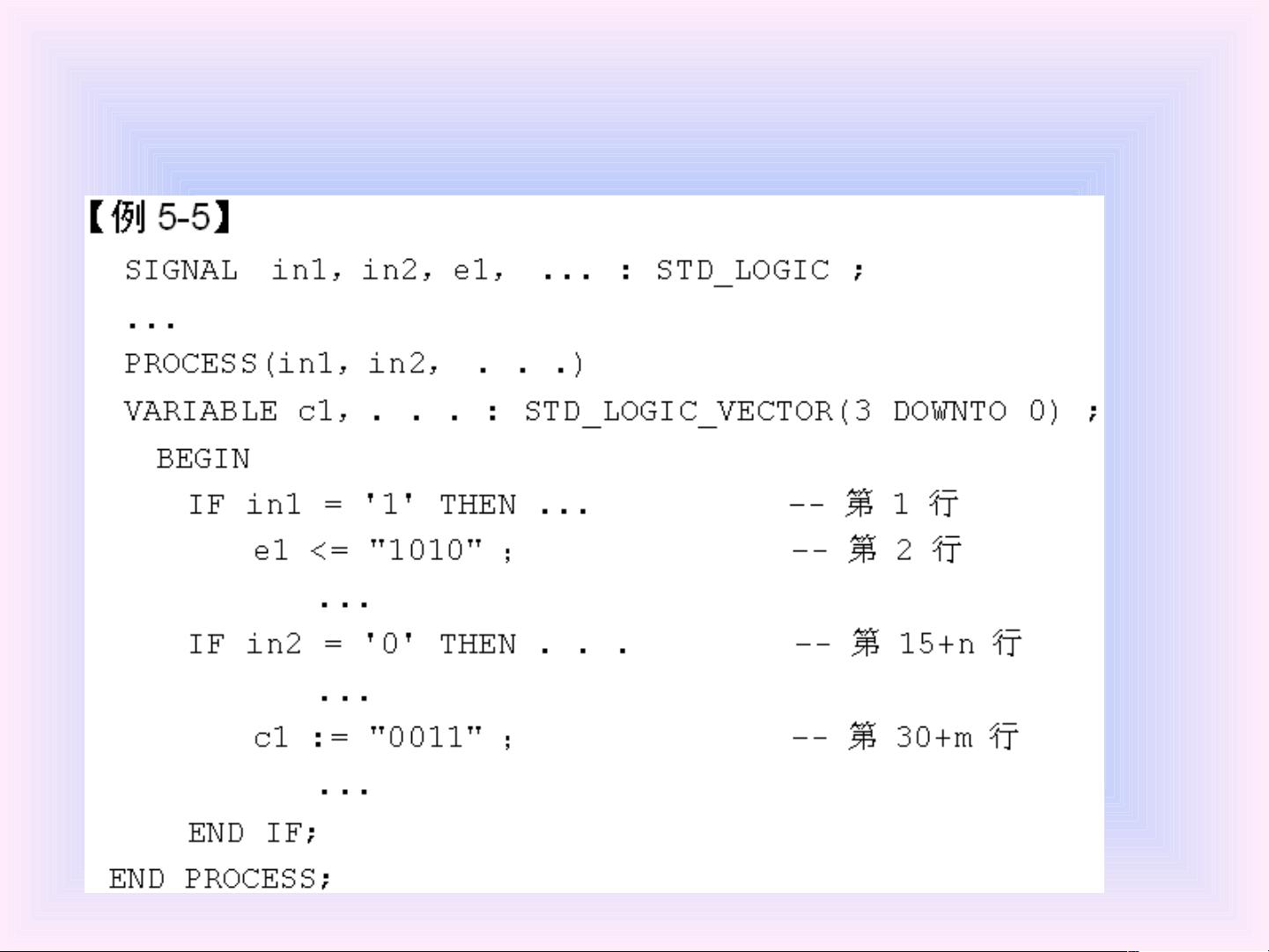

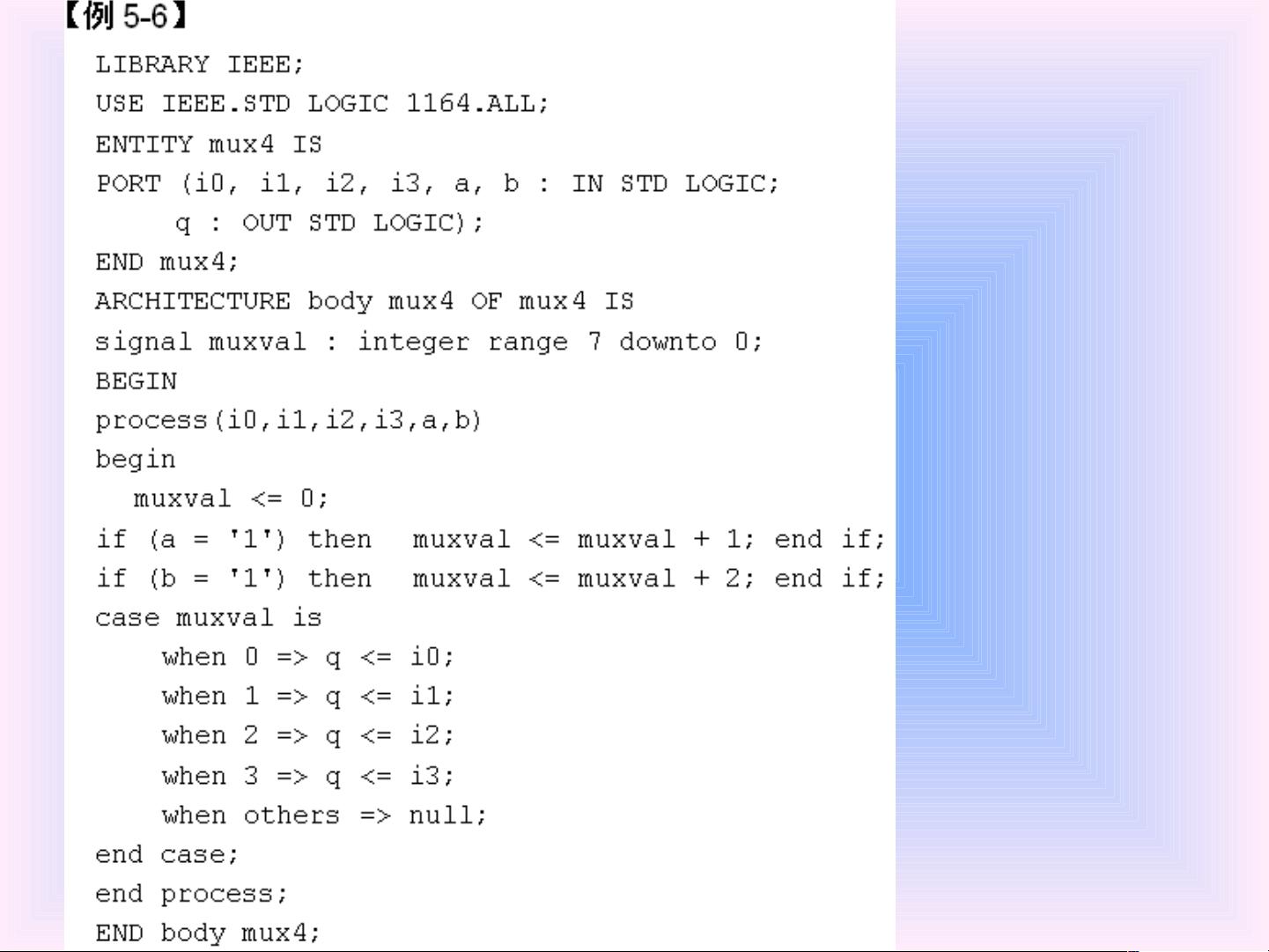

在VHDL的进程中,信号赋值与变量赋值有显著区别。进程是VHDL中实现并发行为的关键构造,它可以包含敏感列表,当列表中的事件发生时,进程将被激活。在进程中,变量赋值是立即完成的,而信号赋值则使用`<=`操作符,表示非阻塞赋值,这种赋值方式不会立即更新信号值,而是等待当前进程的所有其他操作完成后再进行。

接着,通过一系列设计实例,深入解析了VHDL的语法内涵。例如,设计了一个含同步并行预置功能的8位移位寄存器,该设计展示了如何利用VHDL的结构化设计方法来实现复杂的数字逻辑功能。移位寄存器可以按照指定的移位模式进行操作,这通过控制信号实现,体现了VHDL的灵活性。

此外,还介绍了位矢中'1'码个数统计电路的设计,这里涉及到了循环语句的使用,包括单个`LOOP`语句和`FOR_LOOP`语句,这些循环结构在VHDL中用于重复执行一段代码直到满足特定条件。通过这样的设计,我们可以计数二进制序列中'1'的数量。

接着,讲解了三态门的设计,三态门允许输出在高阻态、使能或禁用状态之间切换,这在总线共享和数据传输中非常常见。此外,还详细阐述了双向端口的设计方法,双向端口可以作为输入和输出,这在接口设计和内存访问中非常重要。最后,讨论了三态总线电路设计,这种电路允许多个设备在同一条总线上同时通信。

这些实例和语法内涵的介绍,旨在帮助读者掌握VHDL的高级设计技巧,能够灵活运用VHDL进行复杂的数字系统设计,从而在实际的EDA项目中提高效率和设计质量。通过学习和实践,设计师可以更好地理解和控制硬件行为,实现高效、可靠的可编程逻辑器件设计。

相关推荐