Verilog HDL华为入门教程:基础语法与建模解析

"这是一份华为内部的Verilog HDL入门教程,主要涵盖了Verilog HDL的基本语法、建模方式和一些关键概念。"

本教程详细介绍了Verilog HDL这一广泛用于数字系统设计的硬件描述语言。Verilog HDL是集成电路设计中的一个重要工具,它允许设计师以接近于硬件工作方式的语言描述数字系统的逻辑功能。

1. **Verilog HDL基本语法**(第4章)

- **标识符**(4.1节):在Verilog中,标识符用于命名变量、模块等,必须遵循特定的书写规则。

- **关键词**(4.1.2节):Verilog中的预定义关键字,如`module`, `endmodule`, `reg`, `wire`等,有特定的用途。

- **注释**(4.2节):用于解释代码,有单行和多行两种形式。

- **数据类型**(4.5节):包括线网类型(4.5.1节)和寄存器类型(4.5.2节),如`wire`和`reg`。

- **数值表示**(4.4节):涵盖值集合、常量以及数字值集合的概念。

- **运算符和表达式**(4.6节):包括算术、逻辑、关系和按位逻辑运算符等,用于构建复杂的逻辑表达式。

2. **Verilog HDL建模概述**(第3章)

- **模块**(3.1节):是Verilog设计的基本单元,包含了输入、输出和内部信号。

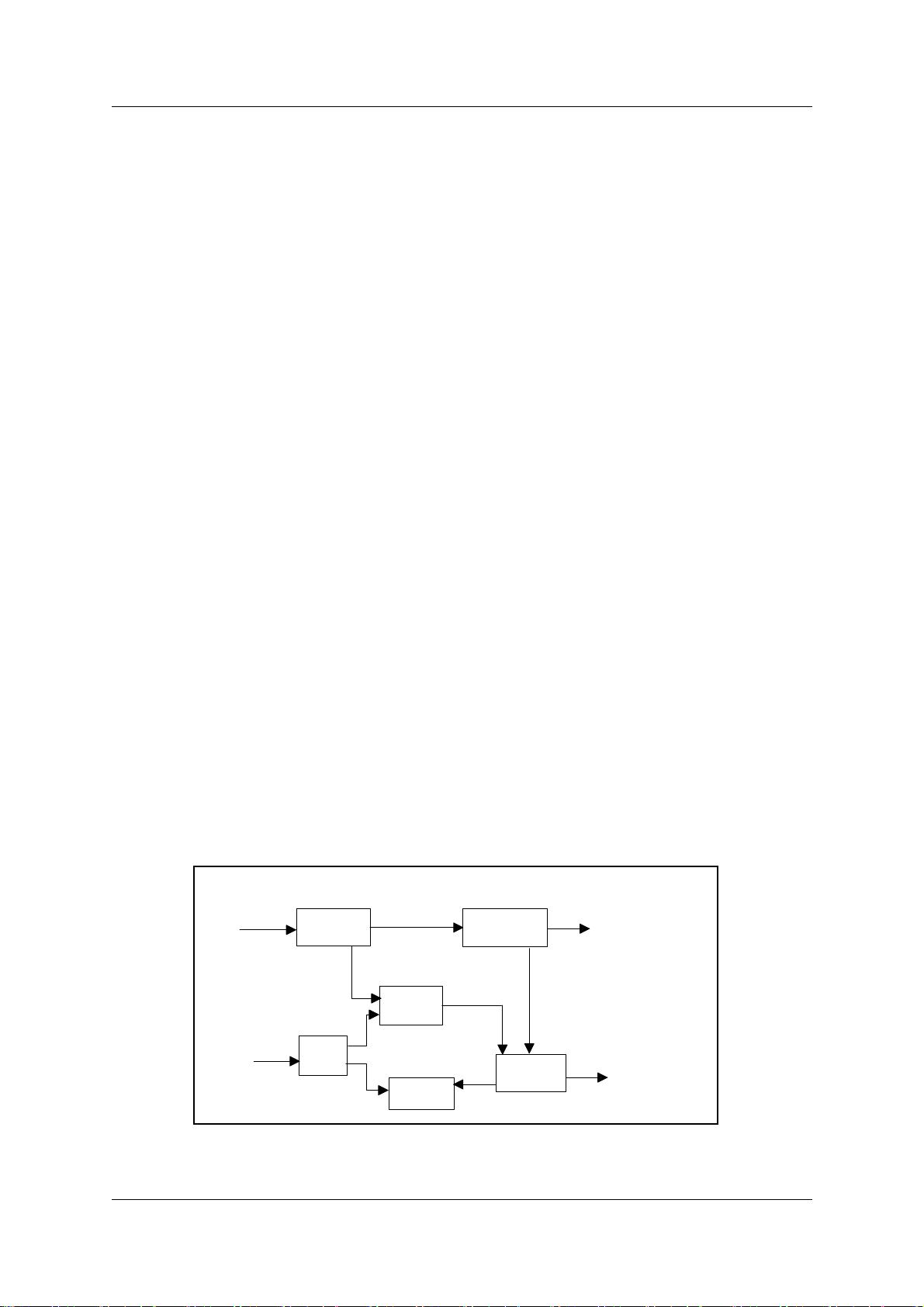

- **结构化描述**(3.3.1节):描述硬件组件的物理连接。

- **数据流描述**(3.3.2节):强调数据的流动,如并行操作。

- **行为描述**(3.3.3节):模拟时序行为,如循环和条件语句。

- **混合设计描述**(3.3.4节):结合以上三种方式,实现更复杂的设计。

3. **建模方式**(第5章)

- **行为建模**(第7章):用类似于高级程序设计语言的方式描述设计的行为,包括顺序语句块(7.2节)、过程赋值语句(7.3节)等。

- **数据流建模**(第6章):通过操作符描述数据的并行处理,有具体的实例分析(6.3节)。

4. **其他方面**(第8章)和**习题**(第9章)提供了对Verilog HDL实际应用的扩展和学习测试。

5. **附录A**(第10章)列出了Verilog HDL的保留字,这对于理解和编写合法的Verilog代码至关重要。

本教程是为初学者设计的,通过逐步讲解Verilog的基础知识,帮助读者掌握这一强大的硬件描述语言,以应用于华为的数字电路设计中。注意,文档标注为“绝密”,意味着它可能包含华为内部的专有信息,仅供内部使用。

1680 浏览量

189 浏览量

250 浏览量

135 浏览量

107 浏览量

2152 浏览量

457 浏览量

271 浏览量

EdisonTao

- 粉丝: 999

最新资源

- VC++挂机锁功能源码解析与下载

- 织梦公司企业通用HTML项目资源包介绍

- Flat-UI:Bootstrap风格的扁平化前端框架

- 打造高效动态的JQuery横向纵向菜单

- 掌握cmd命令:Windows系统下的命令提示符操作指南

- 在Linux系统中实现FTP客户端与服务器的C语言编程教程

- Ubuntu Budgie桌面环境安装全攻略:一键部署

- SAS9.2完整教程:掌握程序与数据集操作

- 精英K8M800-M2主板BIOS更新指南

- OkSocket:Android平台上的高效Socket通信框架

- 使用android SurfaceView绘制人物动画示例

- 提升效率的桌面快捷方式管理工具TurboLaunch

- 掌握AJAX与jQuery技术的全面指南

- Pandora-Downloader:结合Flask实现Pandora音乐下载及管理

- 基于RNN的Twitter情感预测模型:英文推文情绪分析

- 使用Python脚本合并具有相同前缀的PDF文件