www.national.com 16

DP83848I

2.0 Configuration

This section includes information on the various configura-

tion options available with the DP83848I. The configuration

o

ptions described below include:

— Auto-Negotiation

— PHY Address and LEDs

— Half Duplex vs. Full Duplex

— Isolate mode

— Loopback mode

—BIST

2.1 Auto-Negotiation

The Auto-Negotiation function provides a mechanism for

exchanging configuration information between two ends of

a link segment and automatically selecting the highest per-

formance mode of operation supported by both devices.

Fa

st Link Pulse (FLP) Bursts provide the signalling used to

communicate Auto-Negotiation abilities between two

devices at each end of a link segment. For further detail

regarding Auto-Negotiation, refer to Clause 28 of the IEEE

802.3u specification. The DP83848I supports four different

Ethernet protocols (10 Mb/s Half Duplex, 10 Mb/s Full

Duplex, 100 Mb/s Half Duplex, and 100 Mb/s Full Duplex),

so the inclusion of Auto-Negotiation ensures that the high-

est performance protocol will be selected based on the

a

dvertised ability of the Link Partner. The Auto-Negotiation

function within the DP83848I can be controlled either by

internal register access or by the use of the AN_EN, AN1

and AN0 pins.

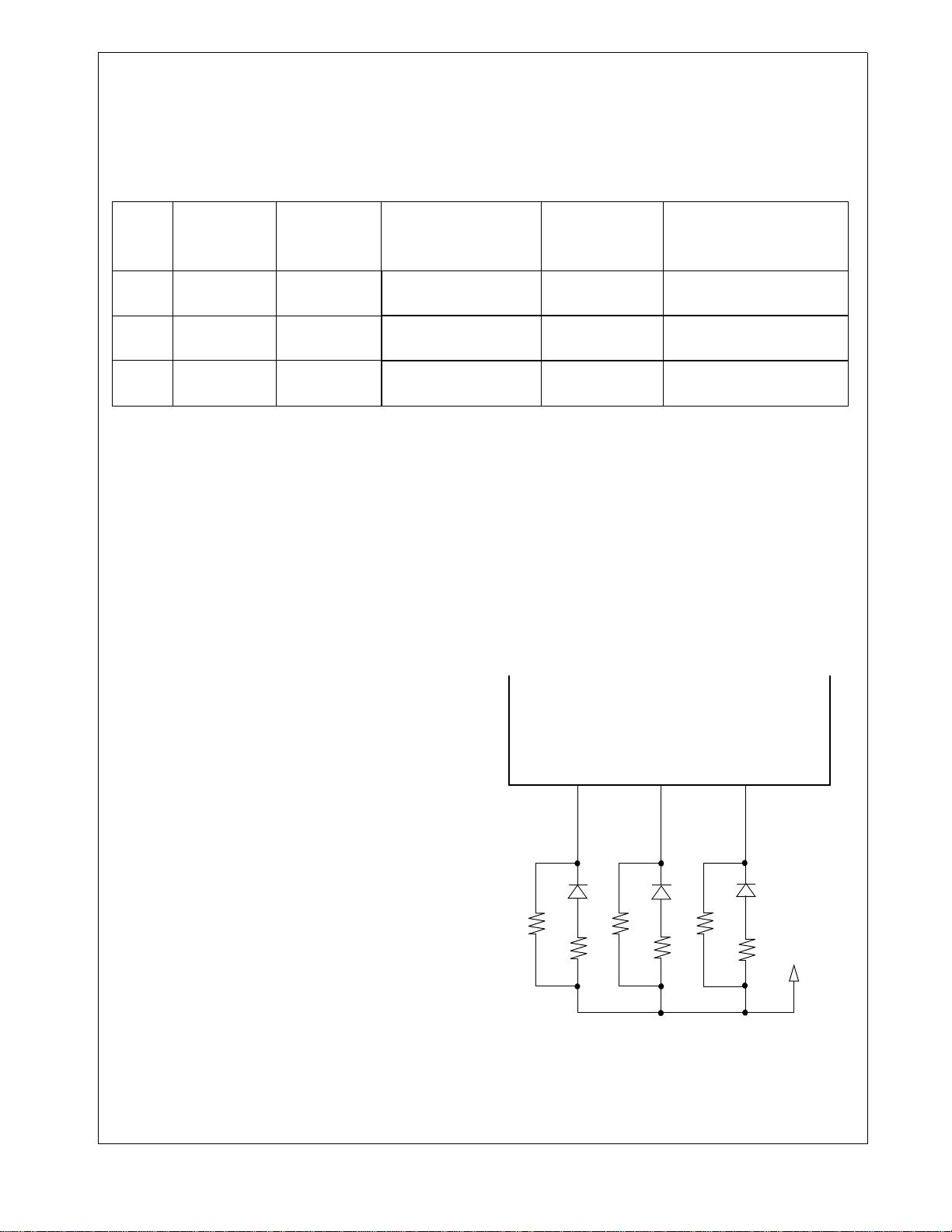

2.1.1 Auto-Negotiation Pin Control

The state of AN_EN, AN0 and AN1 determines whether the

D

P83848I is forced into a specific mode or Auto-Negotia-

tion will advertise a specific ability (or set of abilities) as

g

iven in Table 1. These pins allow configuration options to

be selected without requiring internal register access.

The state of AN_EN, AN0 and AN1, upon power-up/reset,

d

etermines the state of bits [8:5] of the ANAR register.

The Auto-Negotiation function selected at power-up or

r

eset can be changed at any time by writing to the Basic

Mode Control Register (BMCR) at address 0x00h.

2.1.2 Auto-Negotiation Register Control

When Auto-Negotiation is enabled, the DP83848I transmits

t

he abilities programmed into the Auto-Negotiation Adver-

tisement register (ANAR) at address 04h via FLP Bursts.

An

y combination of 10 Mb/s, 100 Mb/s, Half-Duplex, and

Full Duplex modes may be selected.

Auto-Negotiation Priority Resolution:

— (1) 100BASE-TX Full Duplex (Highest Priority)

— (2) 100BASE-TX Half Duplex

— (3) 10BASE-T Full Duplex

— (4) 10BASE-T Half Duplex (Lowest Priority)

The Basic Mode Control Register (BMCR) at address 00h

provides control for enabling, disabling, and restarting the

Auto-Negotiation process. When Auto-Negotiation is dis-

abled, the Speed Selection bit in the BMCR controls

s

witching between 10 Mb/s or 100 Mb/s operation, and the

Duplex Mode bit controls switching between full duplex

operation and half duplex operation. The Speed Selection

and Duplex Mode bits have no effect on the mode of oper-

ation when the Auto-Negotiation Enable bit is set.

The Link Speed can be examined through the PHY Status

R

egister (PHYSTS) at address 10h after a Link is

achieved.

The Basic Mode Status Register (BMSR) indicates the set

of

available abilities for technology types, Auto-Negotiation

ability, and Extended Register Capability. These bits are

permanently set to indicate the full functionality of the

DP83848I (only the 100BASE-T4 bit is not set since the

DP83848I does not support that function).

The BMSR also provides status on:

— Whether or not Auto-Negotiation is complete

— Whether or not the Link Partner is advertising that a re-

mote fault has occurred

— Whether or not valid link has been established

— Support for Management Frame Preamble suppression

The Auto-Negotiation Advertisement Register (ANAR)

i

ndicates the Auto-Negotiation abilities to be advertised by

the DP83848I. All available abilities are transmitted by

default, but any ability can be suppressed by writing to the

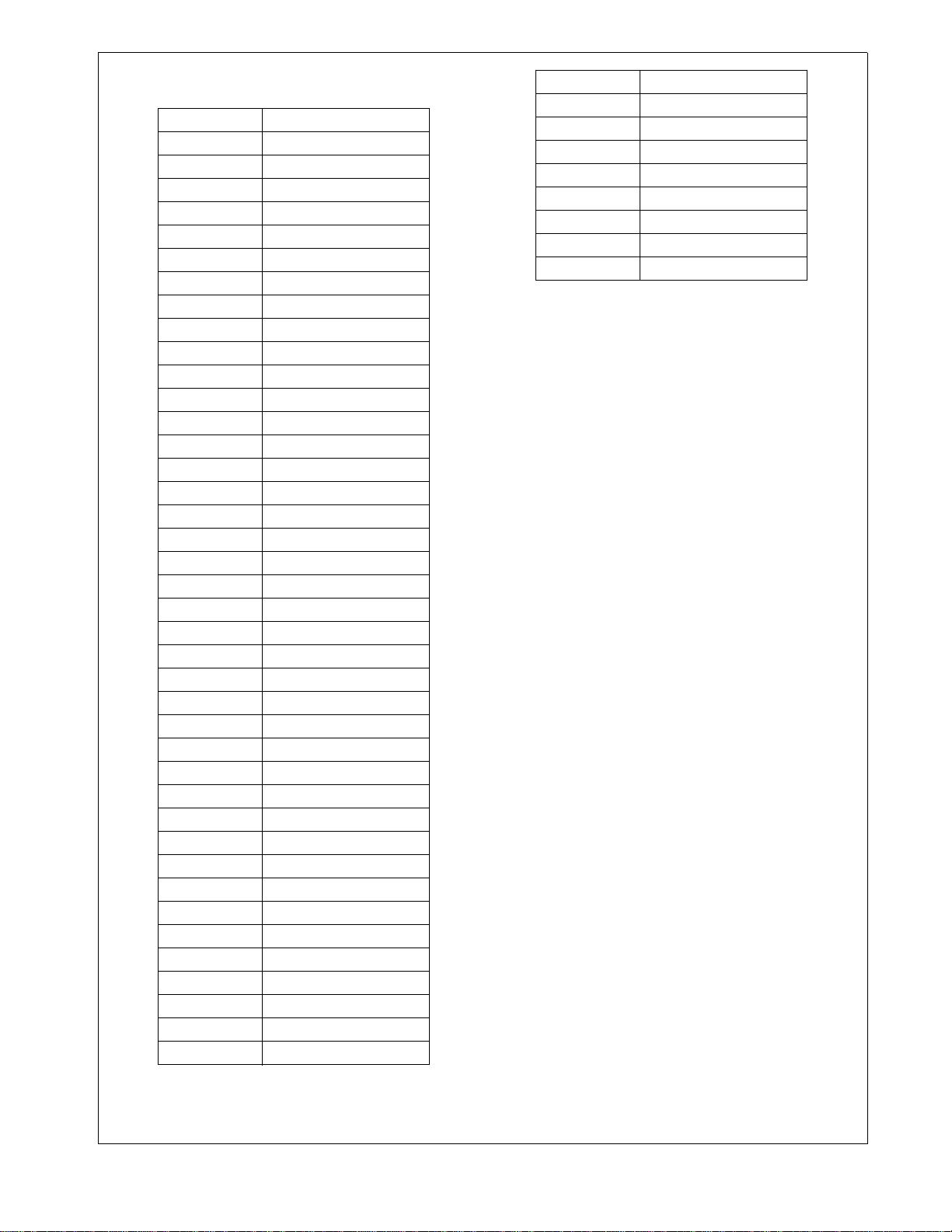

Table 1. Auto-Negotiation Modes

AN_EN AN1 AN0 Forced Mode

0 0 0 10BASE-T, Half-Duplex

0 0 1 10BASE-T, Full-Duplex

0 1 0 100BASE-TX, Half-Duplex

0 1 1 100BASE-TX, Full-Duplex

AN_EN AN1 AN0 Advertised Mode

1 0 0 10BASE-T, Half/Full-Duplex

1 0 1 100BASE-TX, Half/Full-Duplex

1 1 0 10BASE-T Half-Duplex

100BASE-TX, Half-Duplex

1 1 1 10BASE-T, Half/Full-Duplex

100BASE-TX, Half/Full-Duplex