FPGA&ASIC面试必看:笔试试题解析

下载需积分: 18 | PDF格式 | 2.6MB |

更新于2024-07-14

| 91 浏览量 | 举报

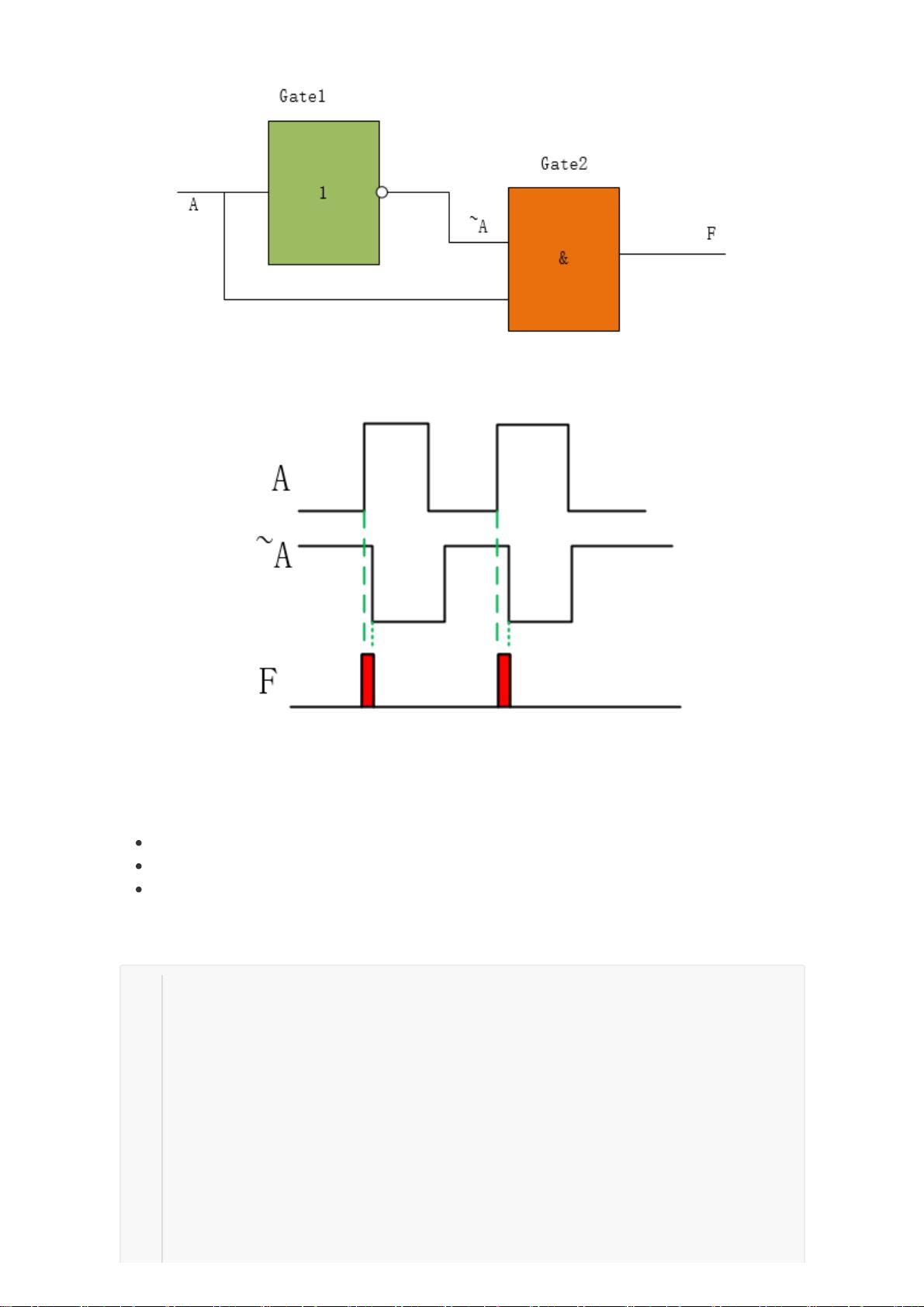

"FPGA&ASIC笔面试题集锦,涵盖了ASIC和FPGA的基本开发流程、数字电路基础知识、逻辑设计、Verilog编程以及时序逻辑电路相关问题,旨在帮助准备IC行业面试的人员复习和巩固相关知识。"

本文将详细讨论在FPGA和ASIC设计中涉及的关键知识点。

1. ASIC设计流程:ASIC(Application-Specific Integrated Circuit)设计通常包括需求分析、逻辑设计、布局布线、仿真验证、物理设计、版图设计、流片制造和测试等多个步骤。工具使用可能包括逻辑综合工具(如Synopsys的Synplify或 Mentor Graphics的ModelSim)、布局布线工具(Cadence的Innovus或Synopsys的ICC)、仿真器(VCS, Questa)等。

2. FPGA开发流程:FPGA开发涉及原理图输入、硬件描述语言(HDL,如Verilog)编程、逻辑综合、适配、布线和下载验证等步骤。常用工具有Xilinx的Vivado、Intel的Quartus II等。

3. 基础概念:

- bit是基本的数据单位,一个bit代表0或1。

- byte由8个bit组成,常用于表示一个字符。

- word的长度根据不同的系统有所不同,通常是16、32或64位。

- dword是双字,等于两个word,通常32位。

- qword是四字,等于四个word,通常64位。

4. 数制转换和逻辑函数化简是数字电路设计的基础,冒险和竞争现象可能导致逻辑错误,可以通过添加适当的缓冲器或使用同步电路来消除。

5. 2-4译码器和BCD译码器是数字逻辑中的常见组件,用于将二进制或BCD编码转换为对应的输出状态。

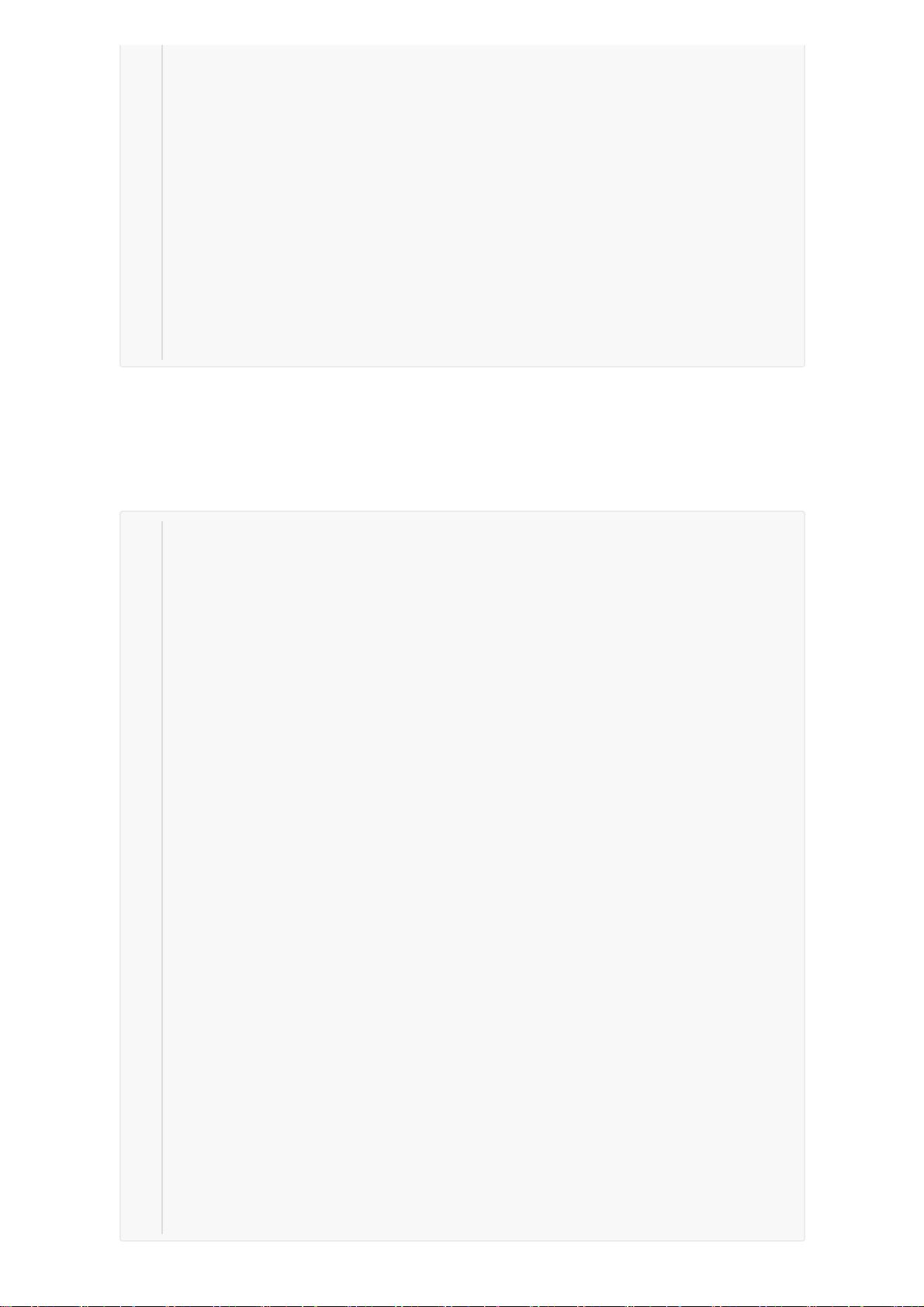

6. MOS逻辑门(如NMOS、PMOS和CMOS)是构建数字电路的基础。

7. Verilog编程中,D触发器与Latch的主要区别在于D触发器在时钟边沿触发更新,而Latch在数据稳定时才捕获。

8. 时序逻辑电路基础包括建立时间和保持时间的概念,同步和异步电路的差异,以及亚稳态的产生和消除方法。

9. Verilog编程中的关键概念,如reg和wire的区别、阻塞与非阻塞赋值、参数定义(localparam、parameter和define)以及task和function的使用场景,对于理解代码行为至关重要。

10. Retiming技术可以优化电路延迟,提高系统性能。

11. 高阻态是指电路元件处于既不导通也不截止的状态,通常在三态门中应用。

12. 跨时钟域设计是FPGA和ASIC中的重要问题,需要正确处理信号同步以避免数据丢失或错误。

13. Verilog代码示例涉及边沿检测、时钟切换、串并转换等功能,这些都是数字系统设计的常见任务。

以上内容仅为部分知识点概述,实际面试可能涉及更深入的技术细节和实际问题解决能力的考察。对于准备FPGA和ASIC面试的个人来说,深入理解和实践这些知识点至关重要。

相关推荐

uestc路人甲

- 粉丝: 1

最新资源

- ASP.NET集成支付宝即时到账支付流程详解

- C++递推法在解决三道经典算法问题中的应用

- Qt_MARCHING_CUBES算法在面绘制中的应用

- 传感器原理与应用课程习题解答指南

- 乐高FLL2017-2018任务挑战解析:饮水思源

- Jquery Ui婚礼祝福特效:经典30款小型设计

- 紧急定位伴侣:蓝光文字的位置追踪功能

- MATLAB神经网络实用案例分析大全

- Masm611: 安全高效的汇编语言调试工具

- 3DCurator:彩色木雕CT数据的3D可视化解决方案

- 聊天留言网站开发项目全套资源下载

- 触摸屏适用的左右循环拖动展示技术

- 新型不连续导电模式V_2控制Buck变换器研究分析

- 用户自定义JavaScript脚本集合分享

- 易语言实现非主流方式获取网关IP源码教程

- 微信跳一跳小程序前端源码解析