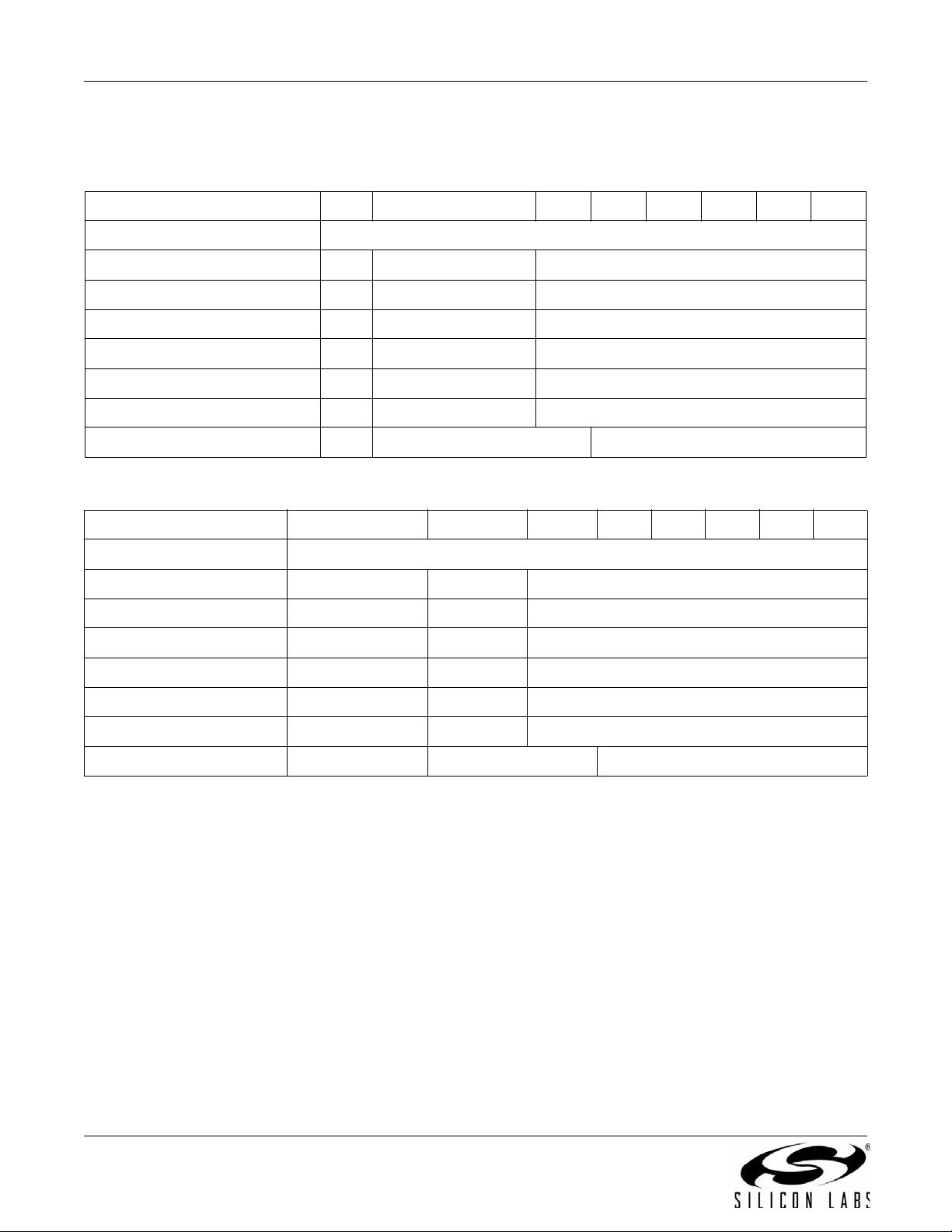

"Si446X API 描述文档提供了对Si446X系列产品的命令和属性的详细解释,用于设备的控制和配置。该文档由Silicon Laboratories出版,适用于Si446X、Si6663和Si4438等产品。文档包含了各种命令的总结,如启动命令、通用命令等,并提供了每个命令的功能概述。" 在Si446X的API中,主要命令包括: 1. Boot Commands(启动命令): - POWER_UP(0x02):用于设备的上电和模式选择,可设置操作功能。 2. Common Commands(通用命令): - NOP(0x00):无操作命令。 - PART_INFO(0x01):报告设备的基本信息。 - FUNC_INFO(0x10):返回设备的功能修订信息。 - SET_PROPERTY(0x11):设置属性值。 - GET_PROPERTY(0x12):检索属性值。 - GPIO_PIN_CFG(0x13):配置GPIO引脚。 - GET_ADC_READING(0x14):获取可能的ADC转换结果。 - FIFO_INFO(0x15):提供访问传输和接收FIFO计数以及重置的功能。 - PACKET_INFO(0x16):返回关于最后接收到的包的信息,并可选择性地覆盖字段长度。 - IRCAL(0x17):校准图像抑制。 - PROTOCOL_CFG(0x18):根据指定的协议设置芯片。 这些命令允许开发者精细控制设备的操作,例如通过PART_INFO获取设备特性,使用SET_PROPERTY和GET_PROPERTY来设置或查询特定属性,通过GPIO_PIN_CFG配置GPIO引脚的用途,或者使用PROTOCOL_CFG来设定通信协议,如蓝牙低功耗(BLE)、Wi-Fi等。 此外,FIFO_INFO命令对于处理数据传输至关重要,因为它允许读取FIFO缓冲区的状态并进行管理。PACKET_INFO则提供了关于接收包的详细信息,这对于调试和优化无线通信链路非常有用。IRCAL命令则是针对无线通信中的干扰抑制进行校准,确保信号质量。 Si446X API描述文档为开发者提供了一个全面的工具集,使他们能够充分利用Si446X系列芯片的功能,进行高效、可靠的无线通信系统设计。通过理解和应用这些API,开发者可以创建定制的通信解决方案,满足不同应用场景的需求。

剩余115页未读,继续阅读

- 粉丝: 3

- 资源: 22

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- OptiX传输试题与SDH基础知识

- C++Builder函数详解与应用

- Linux shell (bash) 文件与字符串比较运算符详解

- Adam Gawne-Cain解读英文版WKT格式与常见投影标准

- dos命令详解:基础操作与网络测试必备

- Windows 蓝屏代码解析与处理指南

- PSoC CY8C24533在电动自行车控制器设计中的应用

- PHP整合FCKeditor网页编辑器教程

- Java Swing计算器源码示例:初学者入门教程

- Eclipse平台上的可视化开发:使用VEP与SWT

- 软件工程CASE工具实践指南

- AIX LVM详解:网络存储架构与管理

- 递归算法解析:文件系统、XML与树图

- 使用Struts2与MySQL构建Web登录验证教程

- PHP5 CLI模式:用PHP编写Shell脚本教程

- MyBatis与Spring完美整合:1.0.0-RC3详解

信息提交成功

信息提交成功