VHDL实现:8位加法器与乘法器设计解析

需积分: 13 43 浏览量

更新于2024-09-21

2

收藏 195KB DOC 举报

"该资源提供了VHDL设计8位加法器和乘法器的实例,包括8位并行加法器的详细设计思路和VHDL源代码。"

在数字系统设计中,VHDL(Virtually Hardware Description Language)是一种广泛应用的硬件描述语言,用于描述数字逻辑系统的结构和行为。本实例主要关注8位加法器的构建,它是数字计算的基础单元,可以扩展应用于更复杂的算术逻辑单元(ALU)。

加法器的类型主要有并行进位和串行进位两种。并行进位加法器在所有位同时进行加法运算,通过进位逻辑处理进位信号,因此运算速度快但资源消耗大。相反,串行进位加法器逐位进行加法运算,进位信号逐位传递,虽然节省资源但速度较慢。对于8位加法器,使用4位并行加法器级联的方式是常见的实现方法,这样可以在速度和资源之间取得平衡。

4位二进制并行加法器的VHDL源代码(ADDER4B.VHD)展示了如何定义实体(ENTITY)和结构体(ARCHITECTURE)。实体定义了输入输出接口,包括低位进位CIN、4位加数A、4位被加数B、4位和S以及进位输出CONT。结构体部分则包含了内部信号的声明和运算逻辑,通过将4位的A和B扩展为5位,然后进行加法运算,得到5位的和SINT,并从中提取4位的和S和进位信号CONT。

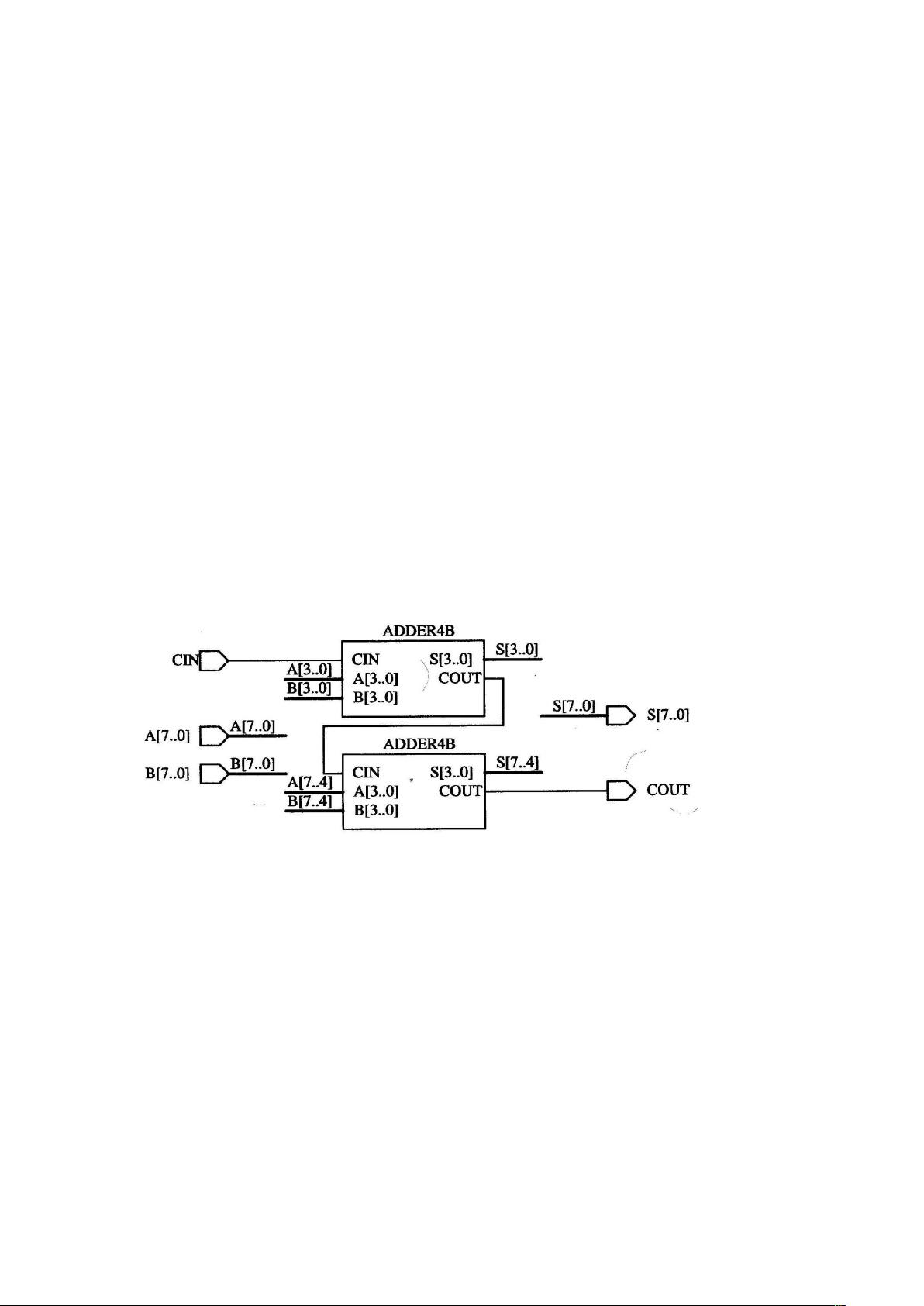

8位加法器(ADDER8B.VHD)的源代码则是两个4位加法器的级联,通过CIN连接两个4位加法器的低位进位,形成8位的加法运算。这种设计方法允许在保持合理速度的同时,有效利用硬件资源。

除了加法器,乘法器也是数字系统中的关键部件,通常可以通过多个加法器和移位操作实现。虽然本资源没有直接涉及乘法器的设计,但理解加法器的工作原理和VHDL实现是构建乘法器的基础。在实际应用中,VHDL使得设计者能够描述硬件的行为,然后通过硬件描述语言综合工具转化为实际的电路设计,广泛应用于FPGA和ASIC设计中。

在VHDL编程时,应注意使用适当的库(如IEEE库),并正确声明数据类型(如STD_LOGIC和STD_LOGIC_VECTOR),以及理解信号(SIGNAL)和变量(VARIABLE)的区别,信号用于通信,而变量则用于临时存储。通过理解这些基本概念,设计师可以有效地编写出高效且符合硬件约束的VHDL代码。

点击了解资源详情

163 浏览量

1419 浏览量

2022-09-23 上传

274 浏览量

2024-06-08 上传

Cooper1111

- 粉丝: 0

- 资源: 1

最新资源

- 作品答辩PPT优质模版.rar

- portfolio-website

- Rcam2:配备LiDAR传感器的iPad Pro远程深度相机

- Nativescript-Template:具有Sidedrawer和Tabview的现代Nativescript-Angular模板

- z-toolz:用于NodeJS开发的工具

- 易语言2D音效

- KOMenuView:简单的可折叠底部菜单

- 【Vue2 + ElementUI】分页el-pagination 封装成公用组件

- zeroexchange-开源

- 无参考代码_无参考图像质量评价_

- sbrunwas.github.io

- nativescript-razorpay:用于nativescript的非官方razorpay插件

- 阅读笔记:读书笔记心得

- MPR New Tab-crx插件

- three-js-meteor:三个带有 Meteor 的 js 动画。 看第四个动画

- mochawesome-report-generator:独立的Mochawesome报告生成器。 只需添加测试数据