Xilinx FPGA设计优化技巧:提升速度与效率

需积分: 9 155 浏览量

更新于2024-07-29

收藏 2.94MB PDF 举报

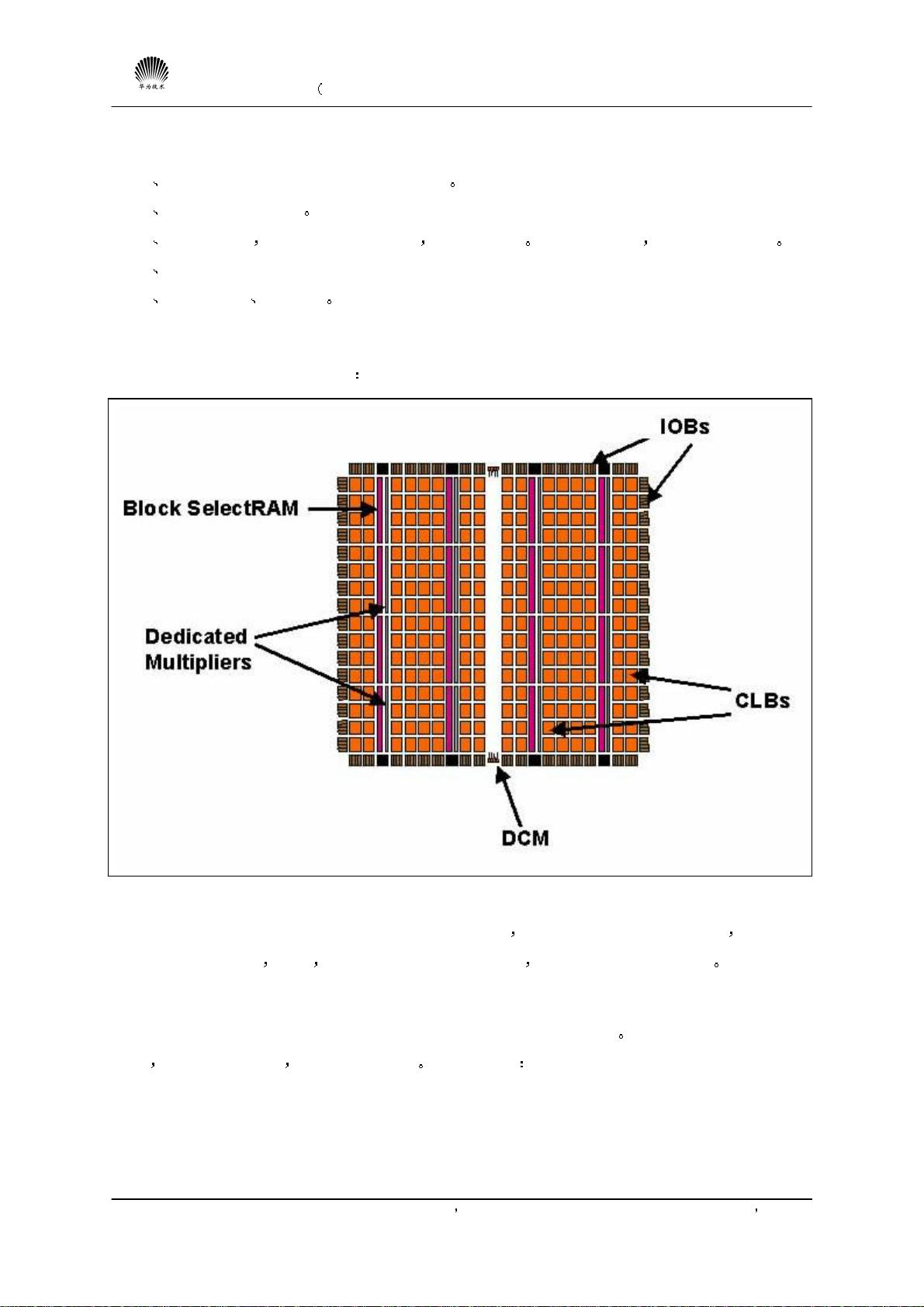

"这份文档是华为内部的一份关于FPGA设计高级技巧的资料,专注于Xilinx FPGA的使用,旨在帮助理解和优化FPGA程序。文档详细介绍了各种设计技巧,包括合理选择加法电路、减少关键路径的逻辑级数、使用IF语句和Case语句等,以提升设计的速度和效率。此外,还深入探讨了FPGA的内部结构,如CLB、LUT、BlockRAM、乘法器资源以及时钟资源的管理,如DCM、CLKMUX等。文档还提到了IOB结构及其配置,以及如何利用这些资源来优化逻辑级数和门数,以实现更快的速度和更小的面积占用。"

本文档首先从FPGA的基础结构出发,介绍了VirtexII系列FPGA的特性,强调了器件结构如何影响编码风格。接着,深入到具体的逻辑单元(CLB)、查找表(LUT)、移位寄存器(SRL)、多路复用器(MUX)等基本元素,讨论了如何通过优化这些单元的使用来改善设计性能。

在内存资源方面,文档涵盖了分布式RAM(DistributedRAM)和块RAM(BlockRAM)的配置和应用,以及如何利用BlockSelectRAM来提高组合逻辑电路的效率。乘法器资源部分,讲解了如何有效地利用乘法器来加速计算过程。

时钟资源管理是FPGA设计中的关键,文档中详细阐述了全局时钟(GlobalClock)、时钟多路复用器(CLKMUX)和数字时钟管理器(DCM)的工作原理和使用策略,以减少时钟路径延迟并提升系统同步性。

在输入/输出(IOB)部分,文档解析了IOB的结构,包括SelectI/O,以及如何配置这些IOB来适应不同的速度和信号完整性要求。

此外,文档还特别关注了如何通过减少关键路径的逻辑级数和使用高效的编程语句(如IF和CASE)来提高设计速度。这些技巧对于优化FPGA程序至关重要,能够帮助设计师在满足性能需求的同时,有效控制硬件资源的使用。

这份文档是FPGA设计者的一份宝贵的参考资料,通过深入理解Xilinx FPGA的内部结构和设计技巧,可以显著提升设计的效率和质量。

105 浏览量

点击了解资源详情

点击了解资源详情

152 浏览量

155 浏览量

126 浏览量

676 浏览量

197 浏览量

Q_Q321

- 粉丝: 1

- 资源: 6

最新资源

- Pokemon-App

- 变焦级镜考勤

- English to Bengali Dictionary | BDWord-crx插件

- ACAM_Demo:工作演员条件注意地图的实时动作检测演示。 此回购包括用于人员检测的完整管道,用于实时跟踪和分析其行为

- FE内容付费系统响应式 带手机版 v5.42

- matlab的slam代码-16-833:机器人定位和地图绘制-2019年Spring[CMU]

- 快乐的地方

- payment-integration-project:作为Sparks Foundation的GRIP实习的一部分,完成了Payment Gateway集成项目

- 一款简单的潜艇大战游戏

- 智睿政务问卷调查系统 v10.9.0

- olive-dolphin-prophecy

- 2019国赛C题资源(1).zip

- ElvishElvis.github.io

- grape-oink:Grape 的中间件,允许使用 Oink

- buyers-remorse-app:一个基于React的Web应用程序,以提高个人对购买选择的认识

- TinyPNG For Photoshop