Verilog红宝书_语法篇:恒创科技详解

需积分: 10 174 浏览量

更新于2024-07-20

收藏 1.43MB PDF 举报

"这是一本由恒创科技出品的Verilog语法学习资料,涵盖了Verilog的基础知识,包括设计方法学、Verilog简介、建模概述、基本语法、结构建模、数据流建模、行为建模等内容,适合初学者和有经验的工程师参考。"

Verilog是一种广泛用于数字系统设计的硬件描述语言(HDL),它允许设计师以结构化、数据流或行为方式来描述电子系统,包括集成电路和系统级设计。这本书《Verilog红宝书_语法篇》由恒创科技出版,作者阿东是一位有着丰富芯片设计经验的专业人士,他在通信行业工作6年,专门从事Verilog编程。

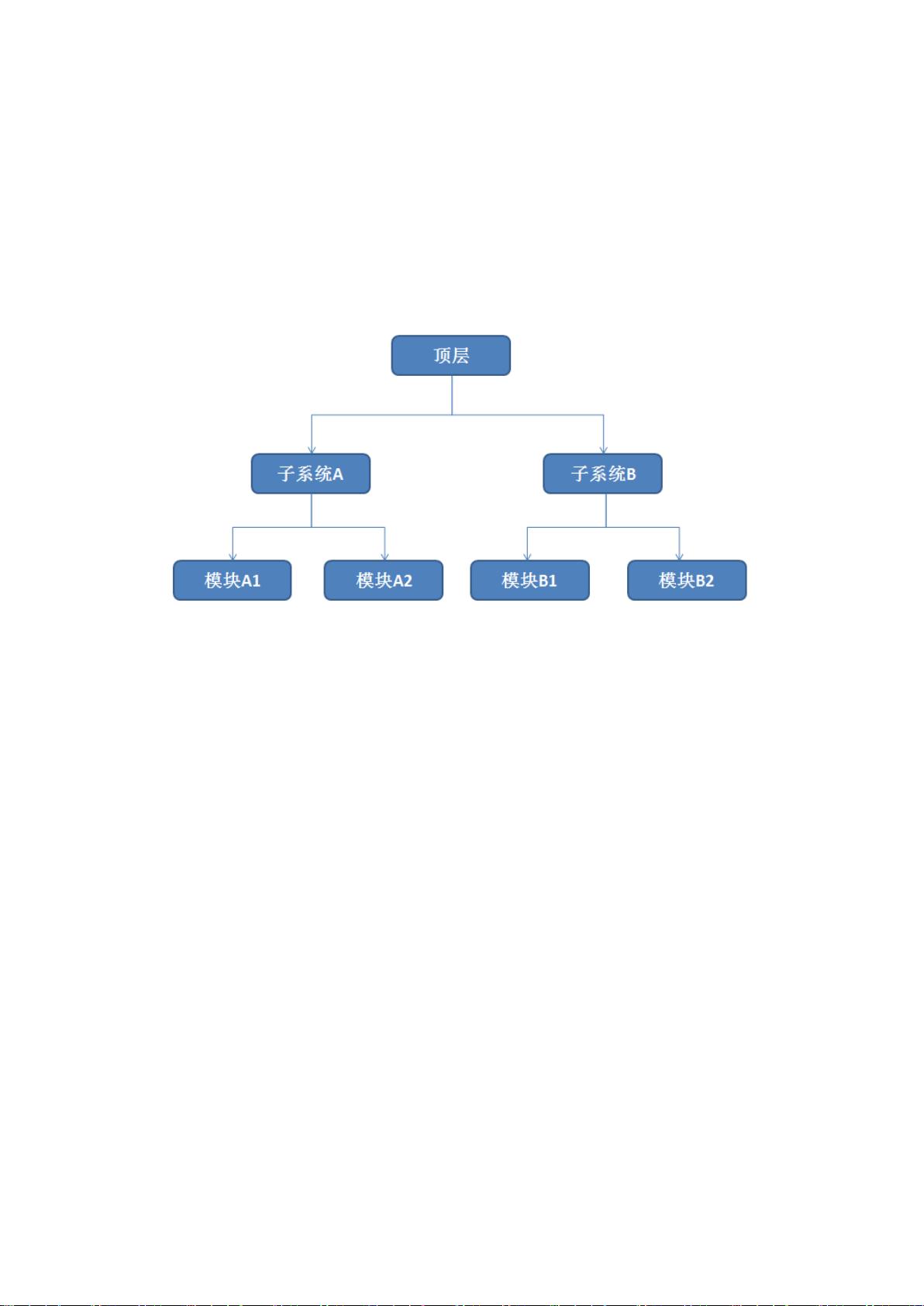

书中首先介绍了设计方法学,讲解了数字电路设计的基本理念以及硬件描述语言在设计流程中的角色。接着,对Verilog进行了简要介绍,阐述了它的功能和用途。在Verilog建模概述部分,详细解析了模块的概念,通过简单例子展示了模块结构、时延处理以及建模的不同方式,如结构化、数据流和行为描述。

在Verilog基本语法章节,书中详细列举了标识符、关键词、书写规范、注释、数字、值集合、常量以及各种数据类型,包括线网类型和寄存器类型。此外,还深入探讨了运算符和表达式,如算术、关系、逻辑和按位逻辑运算符,以及条件和连接运算符。条件语句(如if-else)和case语句的使用也在这一部分进行了阐述。

结构建模部分主要涉及模块定义结构、模块端口、实例化语句,包括例化语法、悬空端口和不同端口长度的处理,以及结构化建模的实际应用示例。

数据流建模则关注连续赋值、阻塞赋值和非阻塞赋值语句的差异与应用,通过实例帮助理解数据流如何在Verilog中实现。

行为建模部分包括顺序语句块、过程赋值语句(如initial和always语句)以及状态机设计,涵盖了Mealy型和Moore型状态机,以及一种常见的三段式状态机设计方法。这部分提供了行为建模的实战案例,有助于读者掌握高级设计技巧。

最后,附录A列出了Verilog的所有保留字,这对于理解和编写合法的Verilog代码至关重要。

这本书是一部详尽的Verilog语法教程,适合初学者入门及专业人士巩固提升,为学习和使用Verilog进行数字系统设计提供了全面的指导。

2010-02-05 上传

2020-04-28 上传

2024-12-27 上传

qq_36253355

- 粉丝: 0

- 资源: 2

最新资源

- matlab拟合差值代码-DMFT:用于单身汉的DMFT代码的最终版本

- 人工智能导论,搜索大作业;2048AI.zip

- date-time-event:一个非常简单的程序包,用于在特定的DateTime触发事件

- 星空流程跟踪编制关联系统源代码

- LanguageCreator:一种自制玩具编程语言。 构造一个AST并验证作用域规则。 具有类型推断功能,支持函数和函数,具有构造函数的类(但无继承),while和for循环,ifelseifelse条件,异常,动态对象等

- My机器学习资料包!!!

- 人工智能导论课程设计-用强化学习玩FlappyBird.zip

- sipp.svn5.zip_Linux/Unix编程_Unix_Linux_

- barba:在您的网站页面之间创建麻烦,流畅和平滑的过渡

- cross-sell-prediction-heorku

- pwtweetar-aframe

- matlab拟合差值代码-teamtracking:团队追踪

- Save-Turtle-Prediction

- 万事俱备

- ms-mattention:关注、收藏插件

- flutter 搭建项目架构