异步FIFO结构与FPGA设计:解决亚稳态与高效传输

需积分: 10 199 浏览量

更新于2024-11-10

收藏 158KB DOC 举报

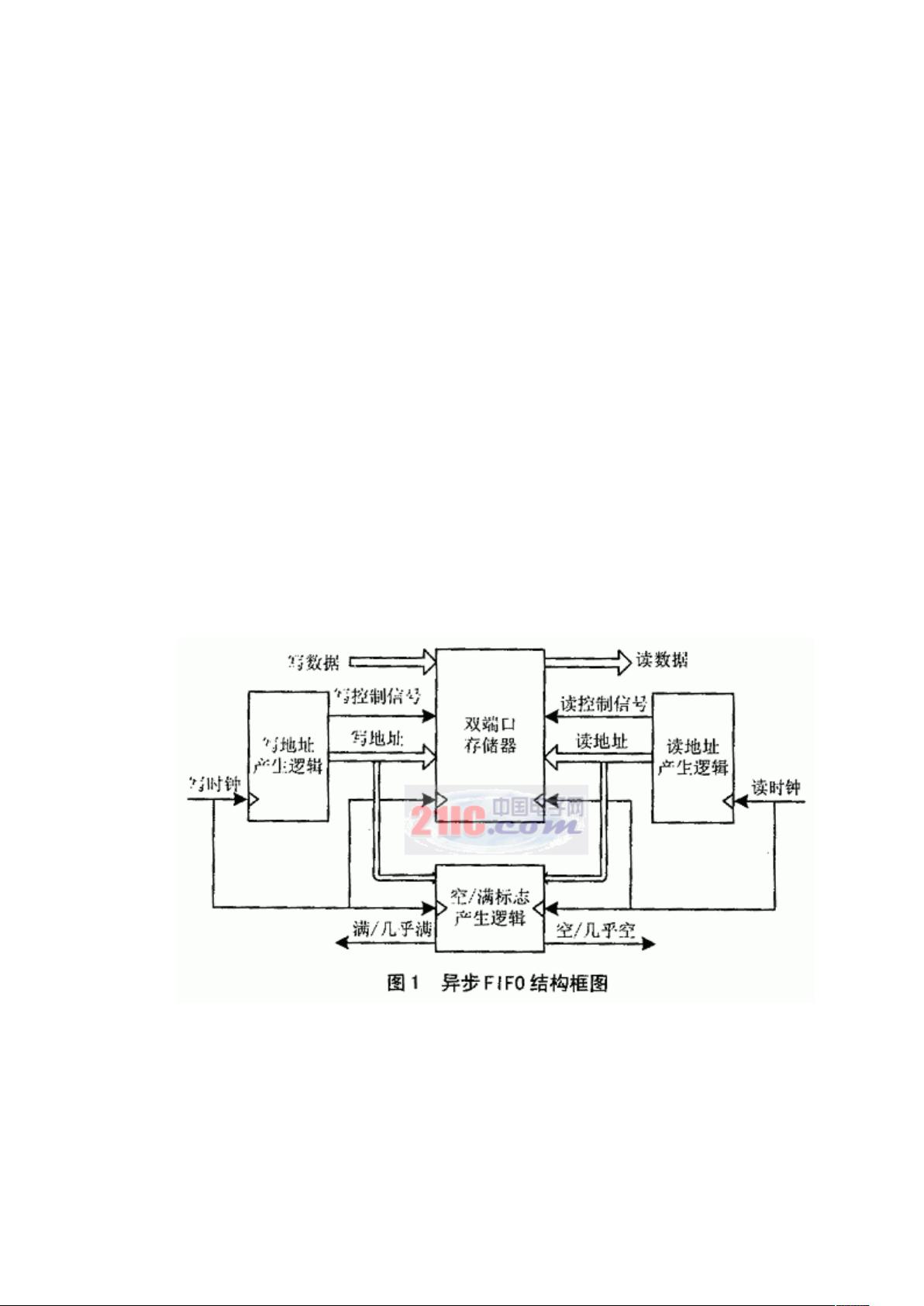

异步FIFO结构及FPGA设计是一篇深入探讨了在现代集成电路中异步电路设计的重要课题,特别是在多时钟域系统中如何实现可靠且高效的异步数据传输。异步FIFO,全称First-In-First-Out,作为一种基本的数据存储单元,用于缓解不同时钟域间的通信问题,确保实时数据的稳定传输。

文章首先介绍了异步FIFO的基本概念和应用,强调了它在诸如网络接口和图像处理等领域的广泛使用。异步FIFO的核心特点是先进先出的工作模式,通过双端口RAM实现读写操作,同时保持两个独立时钟域的同步,避免数据丢失。然而,设计异步FIFO的关键挑战包括如何消除亚稳态问题以及精确管理空、满信号的控制。

亚稳态问题是指在数字电路中,当触发器无法及时响应信号变化时,Q端的值可能会在高电平和低电平之间不稳定,导致数据错误。文章提到,解决这个问题的方法是确保触发器在接收信号时满足setup/hold时间要求,避免时钟和信号之间的不匹配。设计者需要精心设计时钟同步逻辑,确保信号的稳定传输。

另一个难点是空、满信号的控制,这涉及到读写地址的精确比较,以及如何防止几乎满状态下的潜在数据丢失。设计者需要考虑到这些边缘情况,通过适当的电路设计和算法优化来确保正确的数据流。

在实际实现上,文章提出了一个新颖的电路结构,并结合Verilog语言进行了详细的设计和仿真,最后在FPGA平台上进行了验证。通过这种方法,作者克服了异步FIFO设计中的难题,实现了高性能和低错误率的异步数据传输,对于从事FPGA设计和异步电路技术研究的工程师来说具有很高的参考价值。

604 浏览量

473 浏览量

2012-10-30 上传

109 浏览量

2011-03-01 上传

232 浏览量

613 浏览量

130 浏览量

wbb_wjq

- 粉丝: 0

- 资源: 2

最新资源

- iafaqueali.github.io

- VSCodeSetup-x64-1.19.1.exe

- dpletzke:供您阅读!

- SVG灯泡发光特效特效代码

- python代码自动办公 excel处理实例(多工作表合并到单工作表项目源码有详细注解,适合新手一看就懂.rar

- OPC_Runtime_OPCRuntime_OPC运行库文件_

- redpanal:RedPanal网站

- netflix-build

- jetbrains启动报keepass master password is missing的解决办法

- Python项目

- python 自动办公 在Excel表格中将上下行相同内容的单元格自动合并 快速提取一串字符中的中文.rar

- HTML5多立方体3D翻转效果特效代码

- HelloMoon:用于显示图像和播放和停止音频的 Android 应用程序

- PCL官网例程的相关点云数据

- 三菱Q系列PLC CC-Link网络通讯教程 主站从站 主站与远程IO站 远程设备站 视频教程+程序案例+手册资料.zip

- palautusrepositorio:全栈开放库尔西