FPGA时序分析详解:工具与流程

"这份资料详细介绍了FPGA时序分析的相关概念、流程和工具,包括静态时序分析(Static Timing Analysis, STA)以及不同厂商的时序分析工具,如Synopsys的PrimeTime、Mentor Graphics的SST Velocity、Innoveda的Blast和FPGA相关的时序分析软件。资料中还提到了时序路径分析和时序收敛(Timing Closure)等问题,旨在帮助理解和优化FPGA设计的时序性能。"

在FPGA设计中,时序分析是确保电路正确运行的关键步骤。它涉及到对电路延迟的精确计算,以满足预定的设计约束,如时钟周期和建立时间。时序分析分为静态时序分析(Static Timing Analysis, STA)和动态时序分析,但通常在FPGA设计中,我们主要关注静态时序分析。

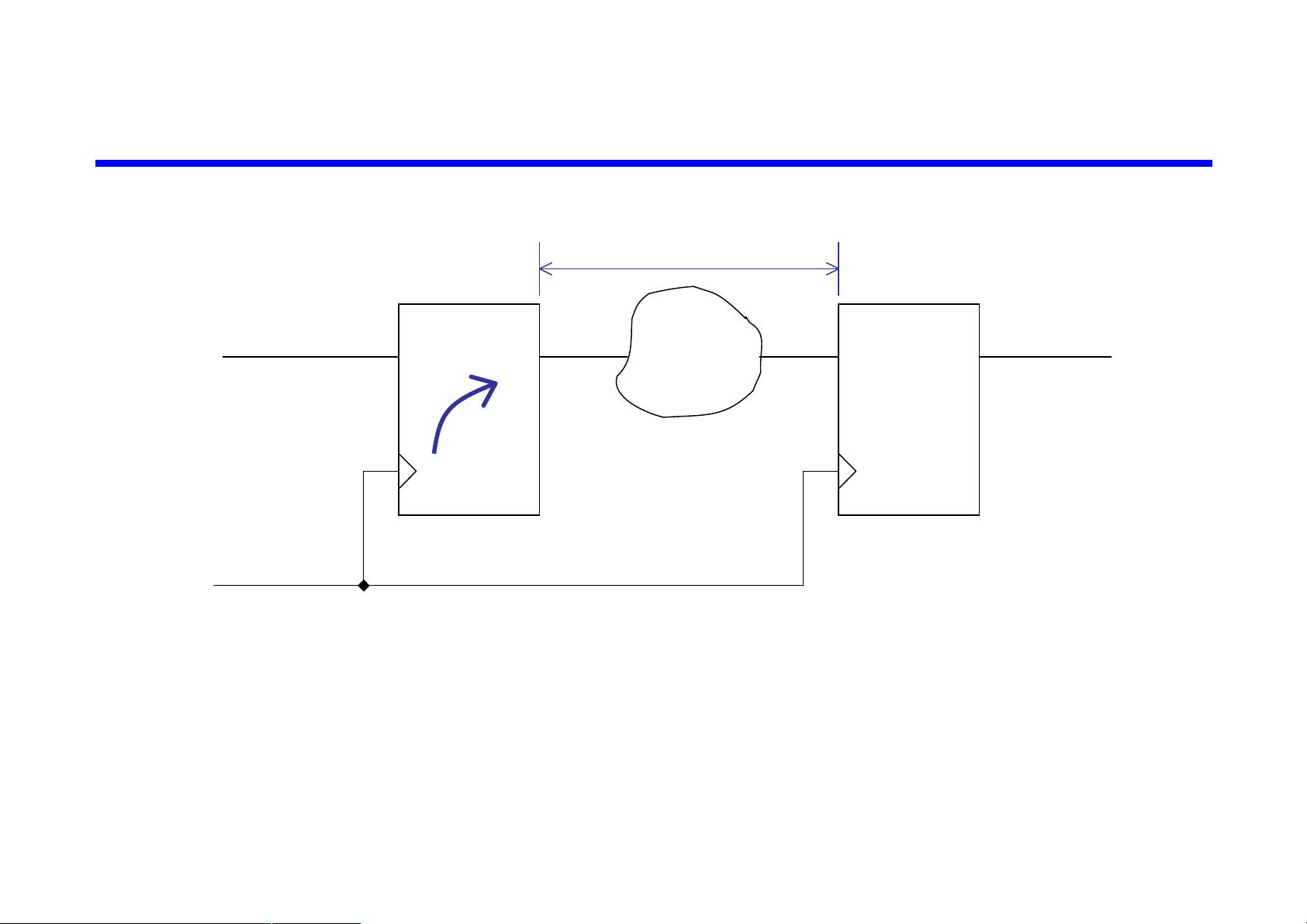

静态时序分析是通过分析电路中的所有路径来确定最慢路径,即路径延迟最长的路径,因为这些路径将决定整个设计的时钟速度。在这个过程中,会考虑逻辑门的延迟、布线延迟以及时钟网络的延迟。STA工具,如Synopsys的PrimeTime或Mentor Graphics的SST Velocity,能够提供详细的报告,显示每个路径的延迟,并帮助工程师识别可能导致时序违规的问题。

在FPGA设计中,路径分析是理解设计性能的重要部分。路径分析包括识别关键路径,这些路径决定了设计的时钟速度。此外,还需要分析负裕量路径,这些路径在最坏情况下可能无法满足时序要求。通过优化这些路径,可以提高设计的整体时序性能。

时序收敛是设计流程中的一个重要目标,意味着所有的时序路径都满足了预设的时序约束。如果不能达到时序收敛,可能需要重新布局、优化逻辑或调整时钟树,以减少路径延迟。在这个过程中,可能需要反复迭代,直到所有路径都满足时序要求。

资料中还提到了一些特定的FPGA时序分析工具,例如Innoveda的Blast89和针对FPGA的其他工具,这些工具通常提供了专门针对FPGA架构的时序分析功能,以适应其特有的并行处理和可配置性。

在进行FPGA时序分析时,除了理解基本概念外,熟悉各种工具的使用和优化技巧也是至关重要的。这包括理解如何设置约束、分析报告以及应用各种优化技术来改善时序性能。通过深入学习这些资料,设计师可以更有效地管理FPGA设计的时序,从而提高设计的成功率和效率。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-02-03 上传

2014-07-16 上传

2022-09-23 上传

2013-08-26 上传

2016-11-11 上传

2021-07-07 上传

chenjiaorong

- 粉丝: 0

- 资源: 1

最新资源

- 火炬连体网络在MNIST的2D嵌入实现示例

- Angular插件增强Application Insights JavaScript SDK功能

- 实时三维重建:InfiniTAM的ros驱动应用

- Spring与Mybatis整合的配置与实践

- Vozy前端技术测试深入体验与模板参考

- React应用实现语音转文字功能介绍

- PHPMailer-6.6.4: PHP邮件收发类库的详细介绍

- Felineboard:为猫主人设计的交互式仪表板

- PGRFileManager:功能强大的开源Ajax文件管理器

- Pytest-Html定制测试报告与源代码封装教程

- Angular开发与部署指南:从创建到测试

- BASIC-BINARY-IPC系统:进程间通信的非阻塞接口

- LTK3D: Common Lisp中的基础3D图形实现

- Timer-Counter-Lister:官方源代码及更新发布

- Galaxia REST API:面向地球问题的解决方案

- Node.js模块:随机动物实例教程与源码解析