FPGA实现QPSK信号源设计详解

该资源主要讨论了如何基于FPGA(Field-Programmable Gate Array,现场可编程门阵列)设计和实现QPSK(Quadrature Phase Shift Keying,正交相移键控)信号源,特别是针对DDS(Direct Digital Synthesis,直接数字频率合成)技术的应用。

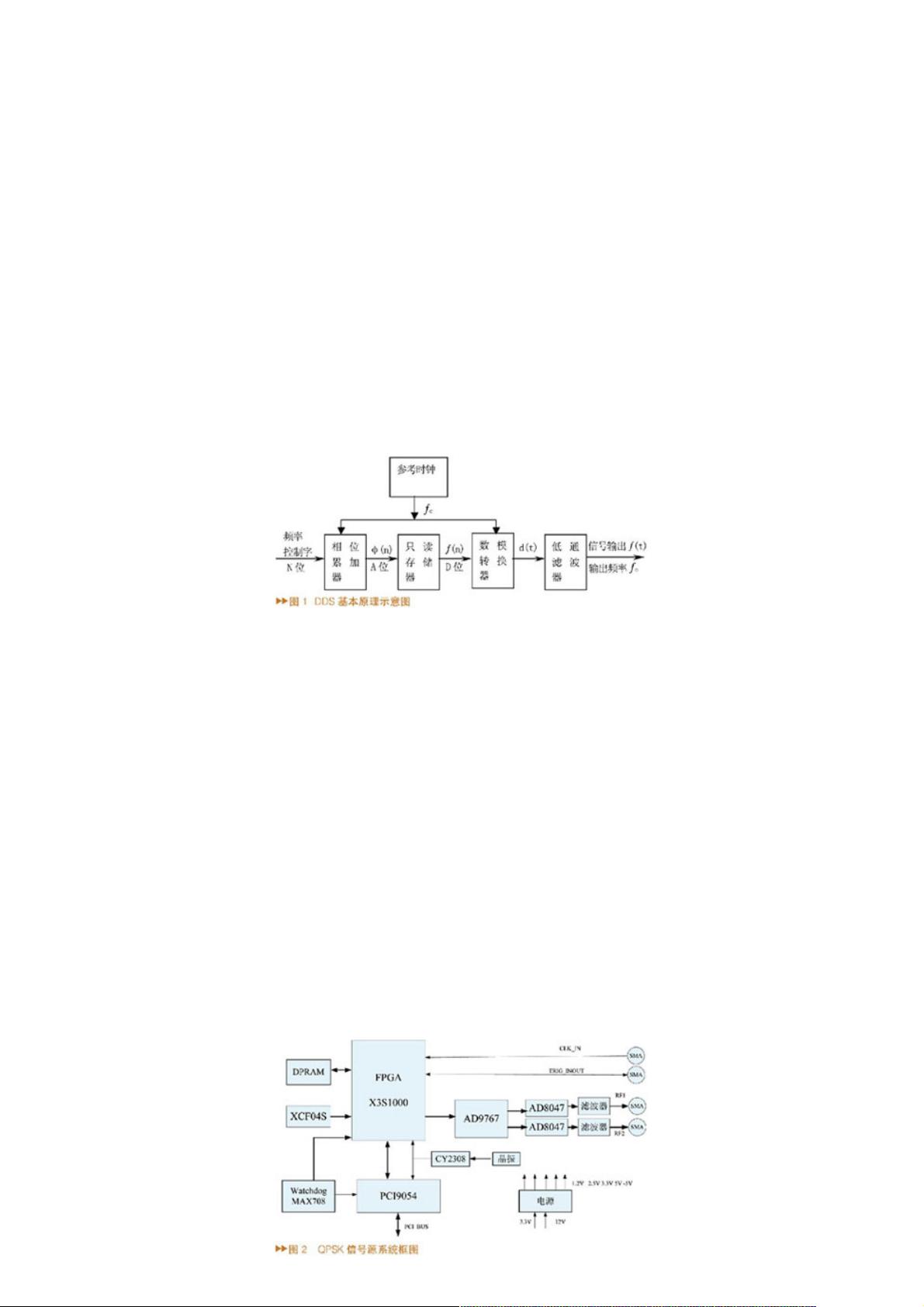

在现代雷达和通信系统中,调相脉冲信号因其优良的压缩比而被广泛使用。DDS技术是一种先进的频率合成方法,通过数字方式控制相位来生成所需频率的信号。DDS的核心包括相位累加器、查找表(ROM)和D/A转换器。其中,相位累加器的输出决定了输出信号的频率,而查找表则根据累加器的输出生成对应的正弦波形。频率分辨率与累加器位数成反比,相位分辨率与ROM地址线位数有关,而幅度量化则受到ROM数据字长和D/A转换器位数的影响。

尽管现有的DDS ASIC芯片如AD9852、AD9854等能方便地产生BPSK(Binary Phase Shift Keying,二进制相移键控)信号,但对QPSK或更高阶的PSK信号生成存在挑战,因为这些信号对控制更新脉冲的精度要求非常高。文章提出了一种使用FPGA实现QPSK信号源的方法,这种方法能灵活地调整信号参数,满足高精度的需求。

QPSK信号源的设计方案中,DDS部分由正弦查找表和相位累加器构成,计数器则用于控制QPSK信号的重复周期。QPSK信号的码元宽度可以通过计数器来设定,并且需要与周期计数器保持同步。此外,参数控制可以通过PCI(Peripheral Component Interconnect,周边组件互连)总线实现,允许外部设备设置QPSK信号的开始、结束、码元数量、重复次数以及码字等参数。

硬件设计部分,文章提到选择了XILINX公司的Spartan3系列XC3S1000 FPGA作为核心器件,该器件拥有足够的BlockRAM和DistributedRAM资源,能够支持复杂的逻辑运算和数据存储需求。通过这种方式,FPGA可以实现高速、灵活的QPSK信号生成,并且能够适应各种不同的系统配置和应用需求。

总结,该文深入探讨了基于FPGA的QPSK信号源设计,结合DDS技术,克服了传统DDS芯片在生成高阶调制信号时的局限性。通过FPGA的灵活性,实现了对QPSK信号的精确控制,这对于雷达和通信系统的性能提升具有重要意义。

2017-03-27 上传

2020-10-20 上传

2023-06-25 上传

2021-07-13 上传

2022-09-24 上传

点击了解资源详情

点击了解资源详情

weixin_38677725

- 粉丝: 5

- 资源: 932

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍