MSP430F5529

,

MSP430F5528

,

MSP430F5527

,

MSP430F5526

MSP430F5525

,

MSP430F5524

,

MSP430F5522

,

MSP430F5521

MSP430F5519, MSP430F5517, MSP430F5515, MSP430F5514, MSP430F5513

www.ti.com

SLAS590M –MARCH 2009–REVISED NOVEMBER 2015

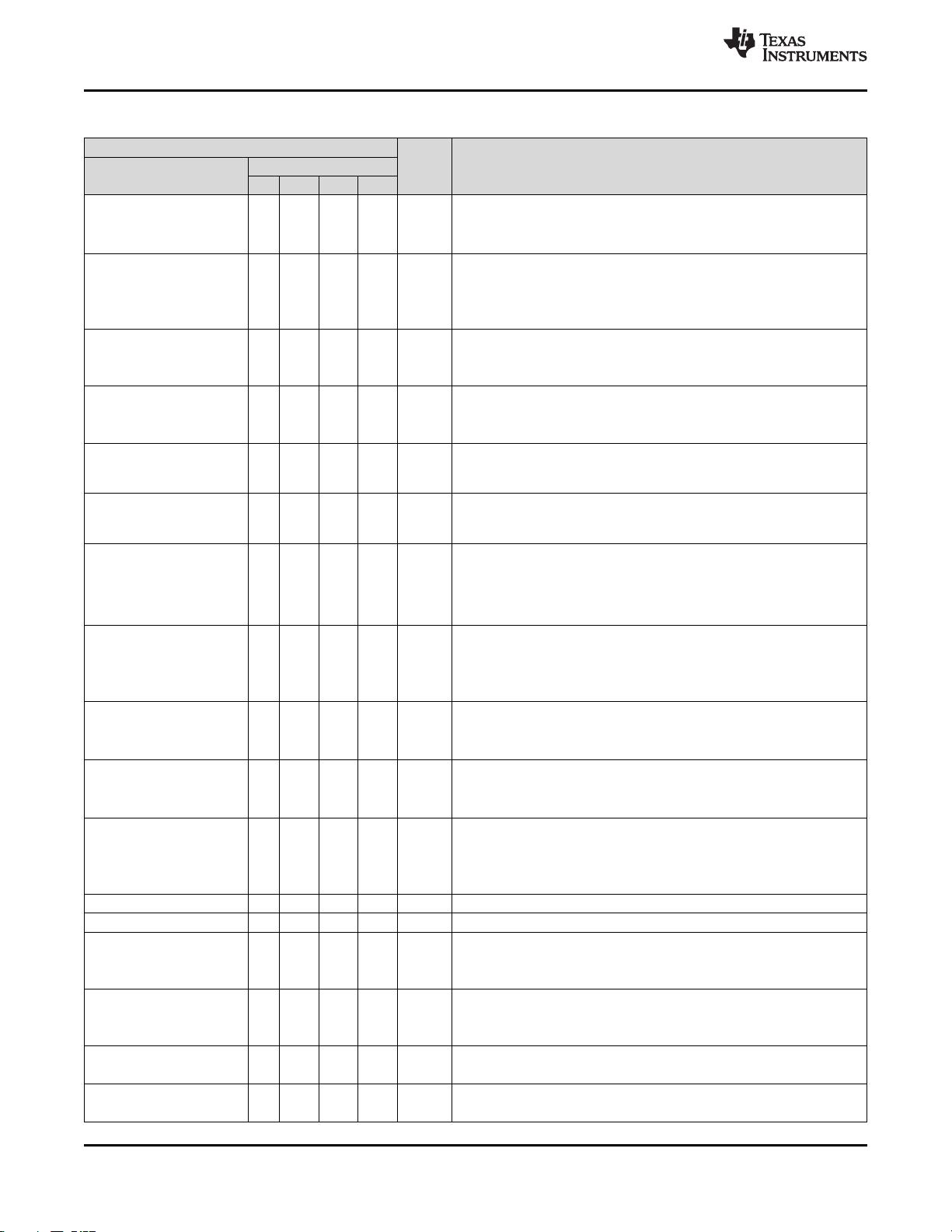

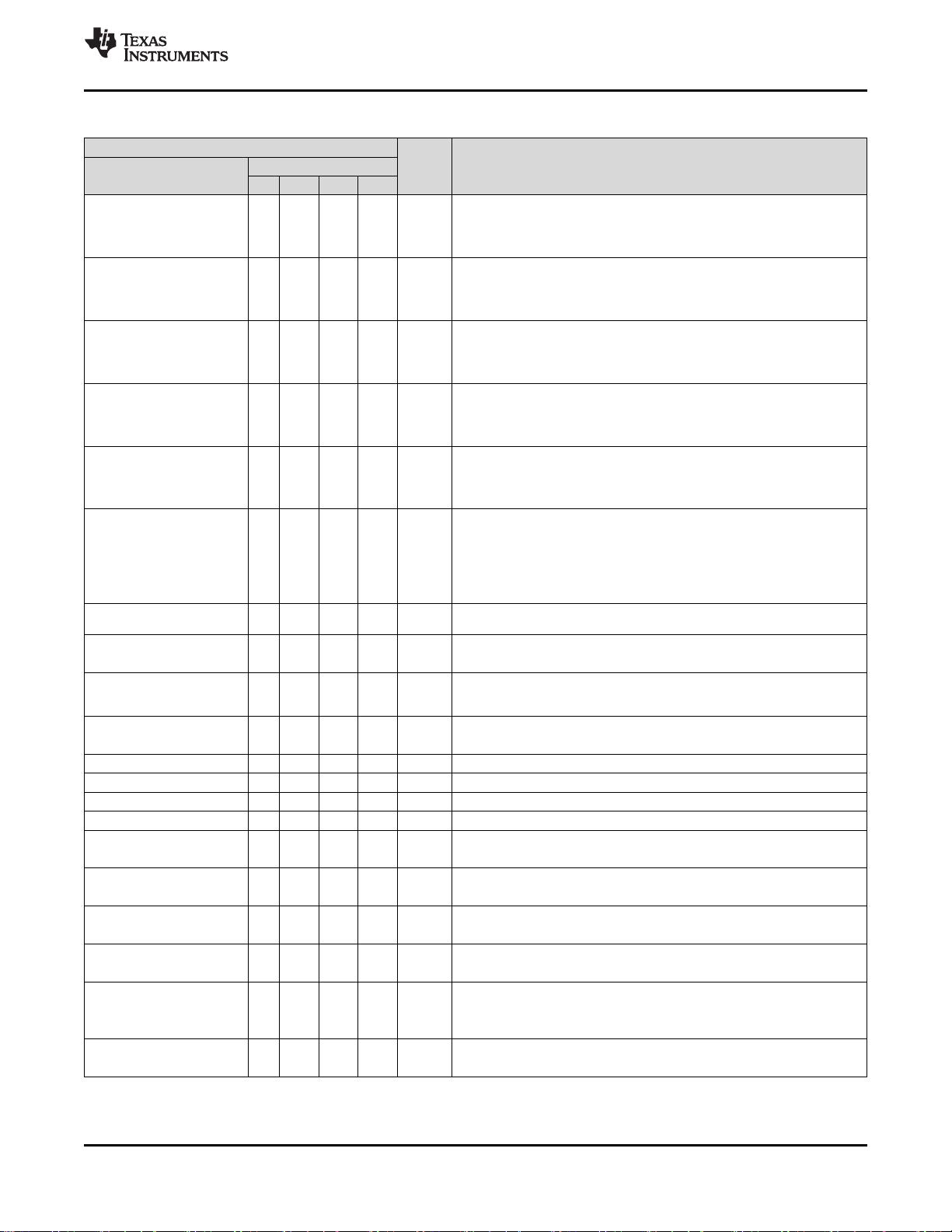

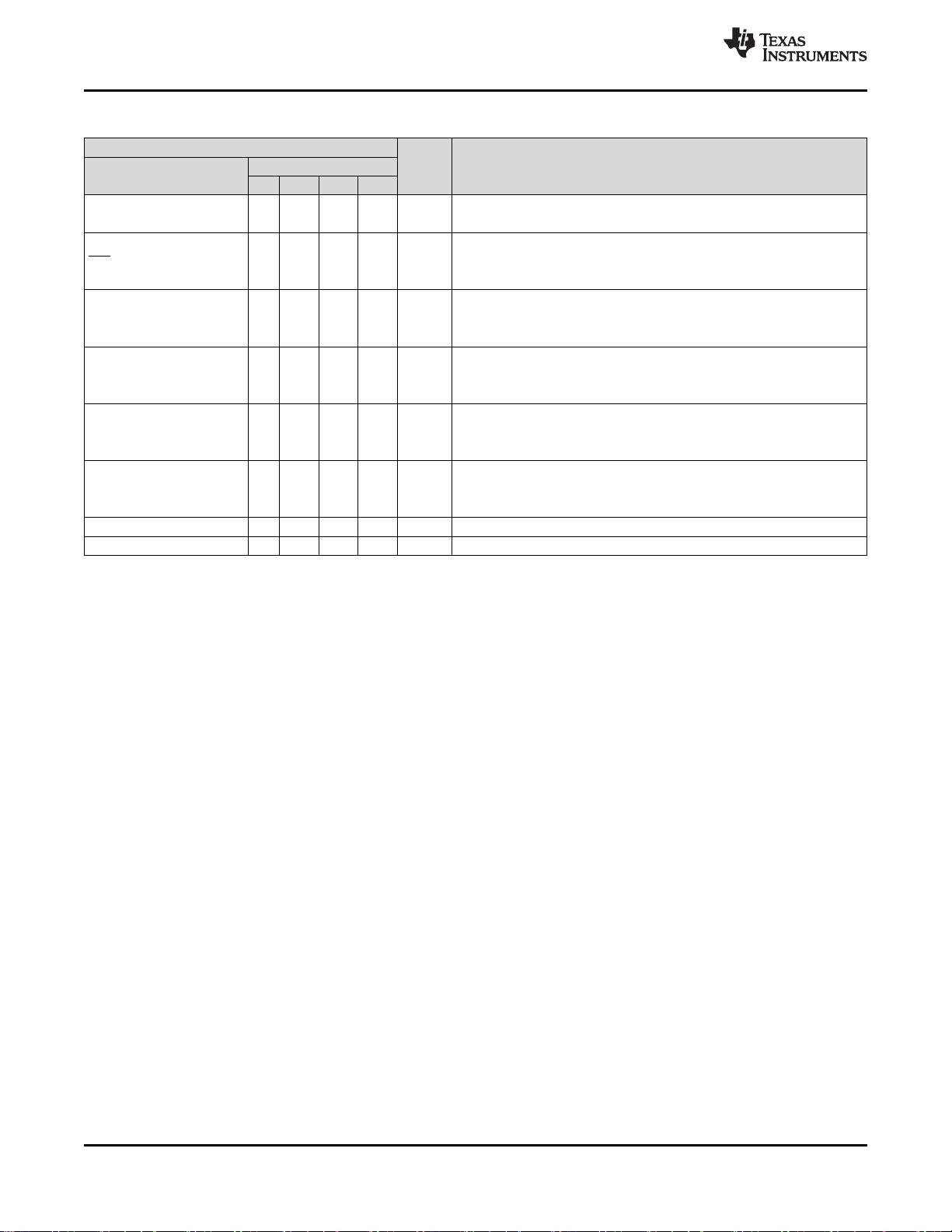

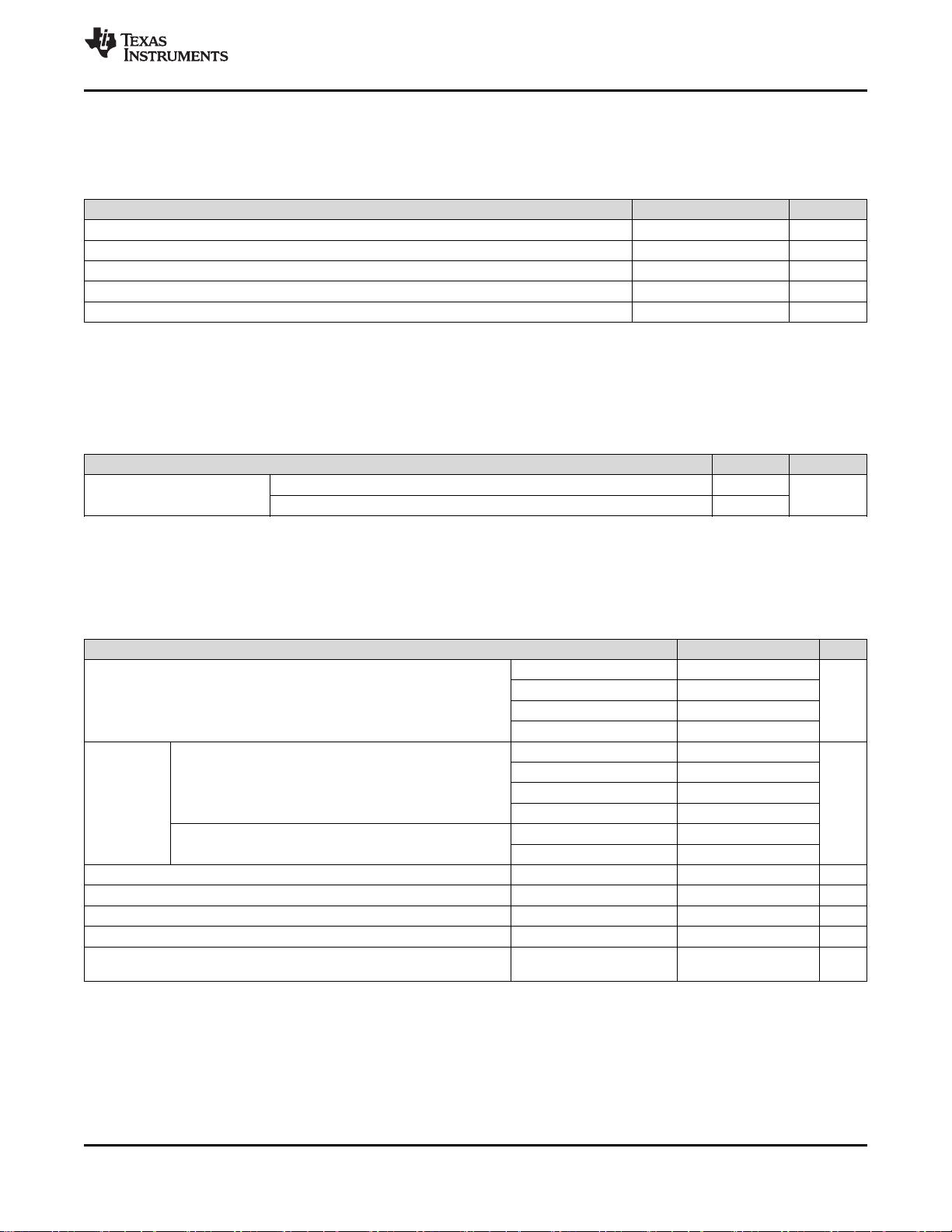

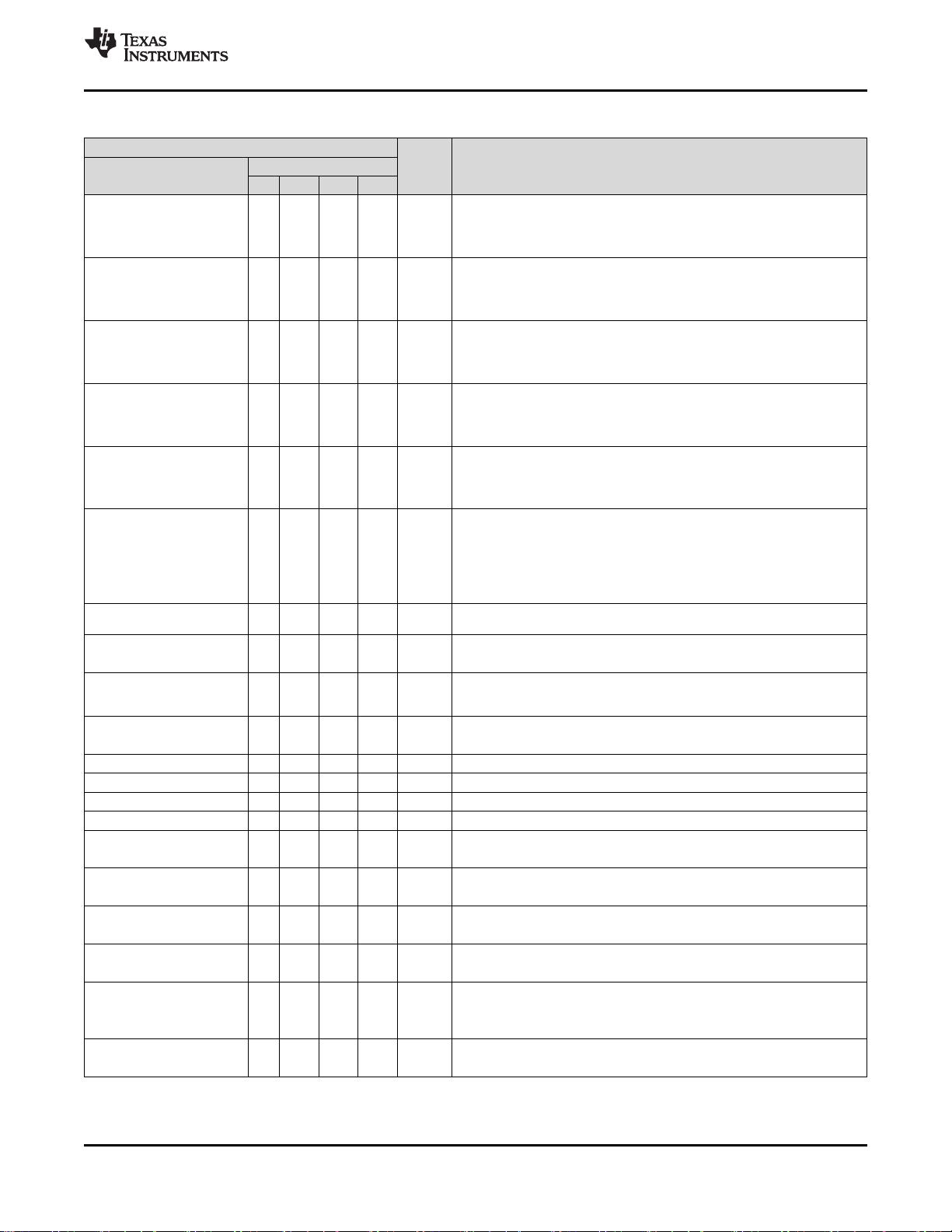

Table 4-1. Terminal Functions (continued)

TERMINAL

NO. I/O

(1)

DESCRIPTION

NAME

PN RGC YFF ZQE

General-purpose digital I/O (not available on F5528, F5526, F5524, F5522, F5514,

F5513 devices)

P5.6/TB0.0 55 N/A N/A N/A I/O

TB0 CCR0 capture: CCI0A input, compare: Out0 output (not available on F5528,

F5526, F5524, F5522, F5514, F5513 devices)

General-purpose digital I/O (not available on F5528, F5526, F5524, F5522, F5514,

F5513 devices)

P5.7/TB0.1 56 N/A N/A N/A I/O

TB0 CCR1 capture: CCI1A input, compare: Out1 output (not available on F5528,

F5526, F5524, F5522, F5514, F5513 devices)

General-purpose digital I/O (not available on F5528, F5526, F5524, F5522, F5514,

F5513 devices)

P7.4/TB0.2 57 N/A N/A N/A I/O

TB0 CCR2 capture: CCI2A input, compare: Out2 output (not available on F5528,

F5526, F5524, F5522, F5514, F5513 devices)

General-purpose digital I/O (not available on F5528, F5526, F5524, F5522, F5514,

F5513 devices)

P7.5/TB0.3 58 N/A N/A N/A I/O

TB0 CCR3 capture: CCI3A input, compare: Out3 output (not available on F5528,

F5526, F5524, F5522, F5514, F5513 devices)

General-purpose digital I/O (not available on F5528, F5526, F5524, F5522, F5514,

F5513 devices)

P7.6/TB0.4 59 N/A N/A N/A I/O

TB0 CCR4 capture: CCI4A input, compare: Out4 output (not available on F5528,

F5526, F5524, F5522, F5514, F5513 devices)

General-purpose digital I/O (not available on F5528, F5526, F5524, F5522, F5514,

F5513 devices)

TB0 clock signal TBCLK input (not available on F5528, F5526, F5524, F5522,

P7.7/TB0CLK/MCLK 60 N/A N/A N/A I/O

F5514, F5513 devices)

MCLK output (not available on F5528, F5526, F5524, F5522, F5514, F5513

devices)

B8,

VSSU 61 49 H2 USB PHY ground supply

B9

General-purpose digital I/O. Controlled by USB control register

PU.0/DP 62 50 H1 A9 I/O

USB data terminal DP

USB pullup resistor pin (open drain). The voltage level at the PUR pin is used to

PUR 63 51 G2 B7 I/O invoke the default USB BSL. Recommended 1-MΩ resistor to ground. See

Section 6.5.1 for more information.

General-purpose digital I/O. Controlled by USB control register

PU.1/DM 64 52 G1 A8 I/O

USB data terminal DM

VBUS 65 53 F2 A7 USB LDO input (connect to USB power source)

VUSB 66 54 F1 A6 USB LDO output

V18 67 55 E2 B6 USB regulated power (internal use only, no external current loading)

AVSS2 68 56 D2 A5 Analog ground supply

General-purpose digital I/O

P5.2/XT2IN 69 57 E1 B5 I/O

Input terminal for crystal oscillator XT2

General-purpose digital I/O

P5.3/XT2OUT 70 58 D1 B4 I/O

Output terminal of crystal oscillator XT2

Test mode pin – Selects four wire JTAG operation

TEST/SBWTCK

(3)

71 59 E3 A4 I

Spy-Bi-Wire input clock when Spy-Bi-Wire operation activated

General-purpose digital I/O

PJ.0/TDO

(4)

72 60 D3 C5 I/O

JTAG test data output port

General-purpose digital I/O

PJ.1/TDI/TCLK

(4)

73 61 D4 C4 I/O JTAG test data input

Test clock input

General-purpose digital I/O

PJ.2/TMS

(4)

74 62 C1 A3 I/O

JTAG test mode select

(3) See Section 6.5 and Section 6.6 for use with BSL and JTAG functions.

(4) See Section 6.6 for use with JTAG function.

Copyright © 2009–2015, Texas Instruments Incorporated Terminal Configuration and Functions 17

Submit Documentation Feedback

Product Folder Links: MSP430F5529 MSP430F5528 MSP430F5527 MSP430F5526 MSP430F5525 MSP430F5524

MSP430F5522 MSP430F5521 MSP430F5519 MSP430F5517 MSP430F5515 MSP430F5514 MSP430F5513