集成电路版图设计详解:Cadence Virtuoso与工艺规则

集成电路版图设计是微电子工业中至关重要的一个环节,它涉及到芯片制造过程中的物理实现。本章节深入探讨了版图设计的各个方面,包括但不限于以下几个关键知识点:

1. **工艺流程定义**:

版图设计首先需要理解工艺流程,即设计者如何通过抽象工艺层来指导实际芯片制造。这些工艺层并非直接对应于掩模层,而是通过逻辑运算转换得到。例如,TSMC的0.35μm工艺中,沟道尺寸、金属布线层数以及对应的电源电压等参数对于电路性能至关重要。

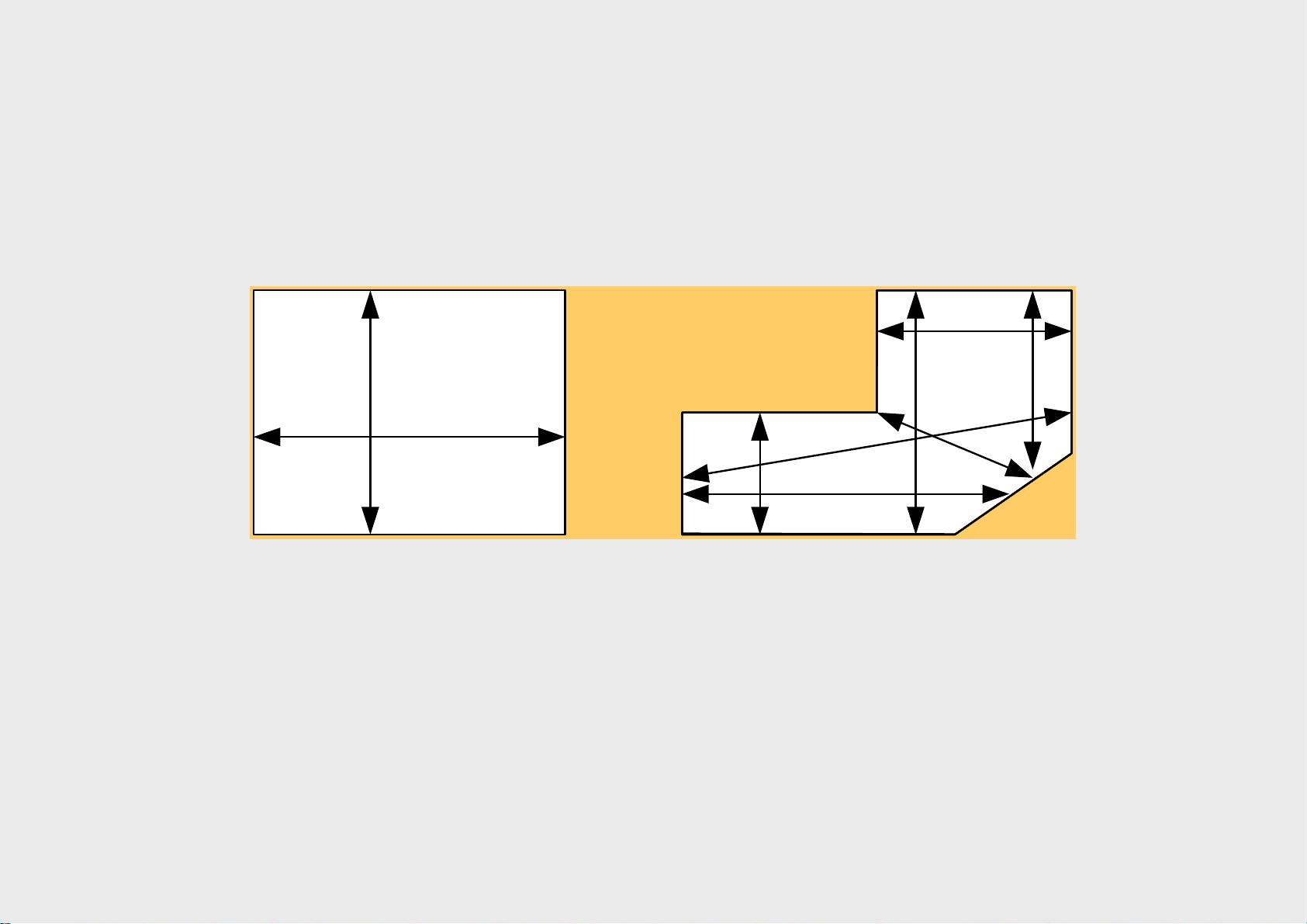

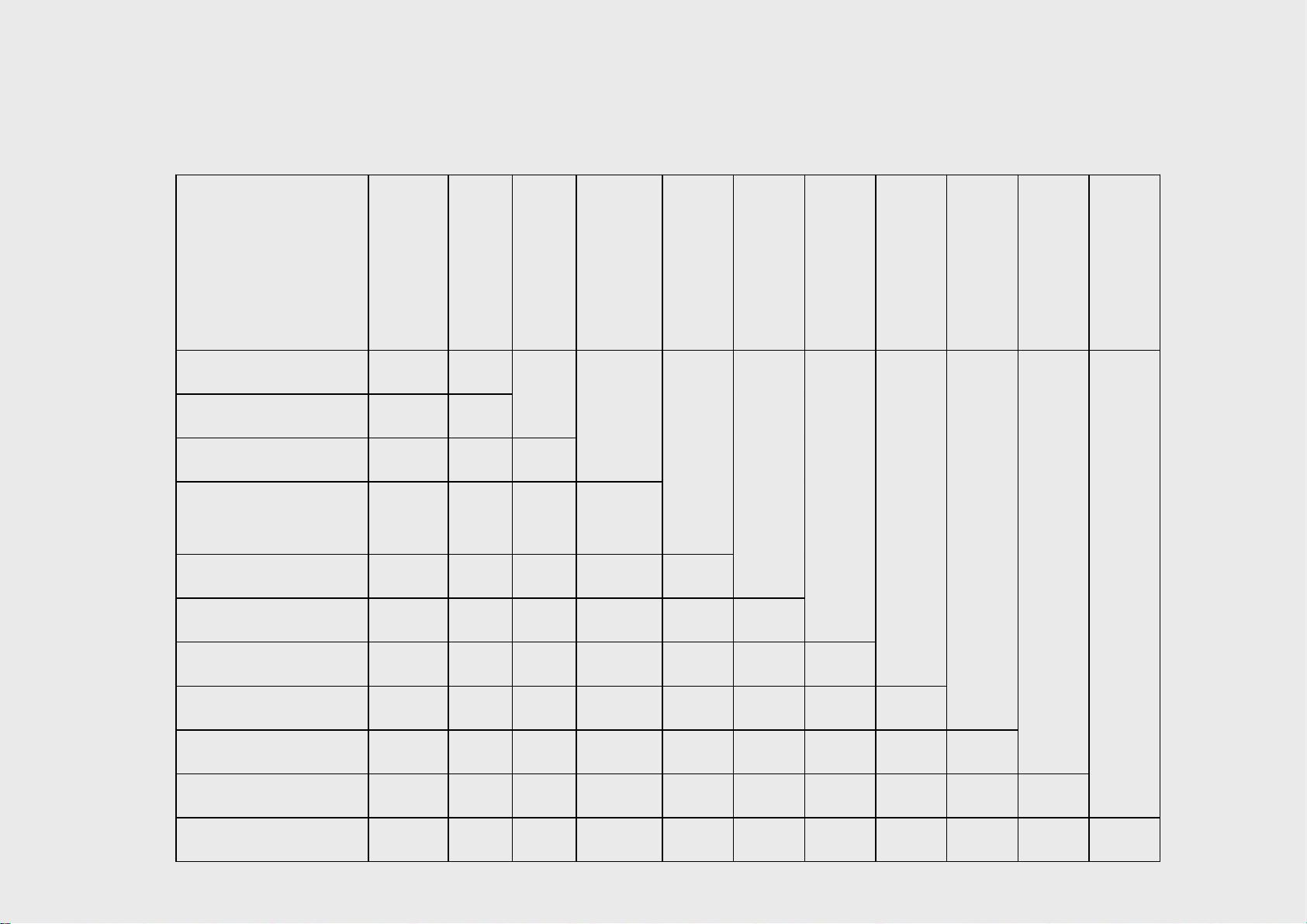

2. **版图几何设计规则**:

版图设计必须遵循严格的几何规则,这些规则是由集成电路制造商根据自身的制造技术制定的。不同的工艺技术,如MOSIS为TSMC的0.35μm CMOS工艺,其具体的工艺层定义和要求会有所差异。

3. **版图图元**:

图元是构成版图的基本元素,包括接触孔、有源层、扩散区等,它们定义了电路元件的物理形态和连接方式。例如,N_well(N阱)、Poly(多晶硅)和Metal1(第一层金属)等图元在设计过程中具有重要作用。

4. **版图设计准则**:

设计者需遵循一系列准则,确保版图的完整性、一致性以及可制造性。这些准则涉及尺寸约束、信号完整性、噪声控制等方面,以保证芯片在实际生产中的性能和可靠性。

5. **电学设计规则与布线**:

版图设计不仅要考虑几何布局,还要考虑电学特性,如电源分配网络(VCC、GND)、信号路径的布线长度和阻抗匹配等,以确保信号的传输质量和功率消耗。

6. **Cadence平台的应用**:

Cadence Design System,特别是其Virtuoso工具,是业界广泛使用的版图设计工具,它提供了图形化的界面,方便设计者进行版图绘制和优化。

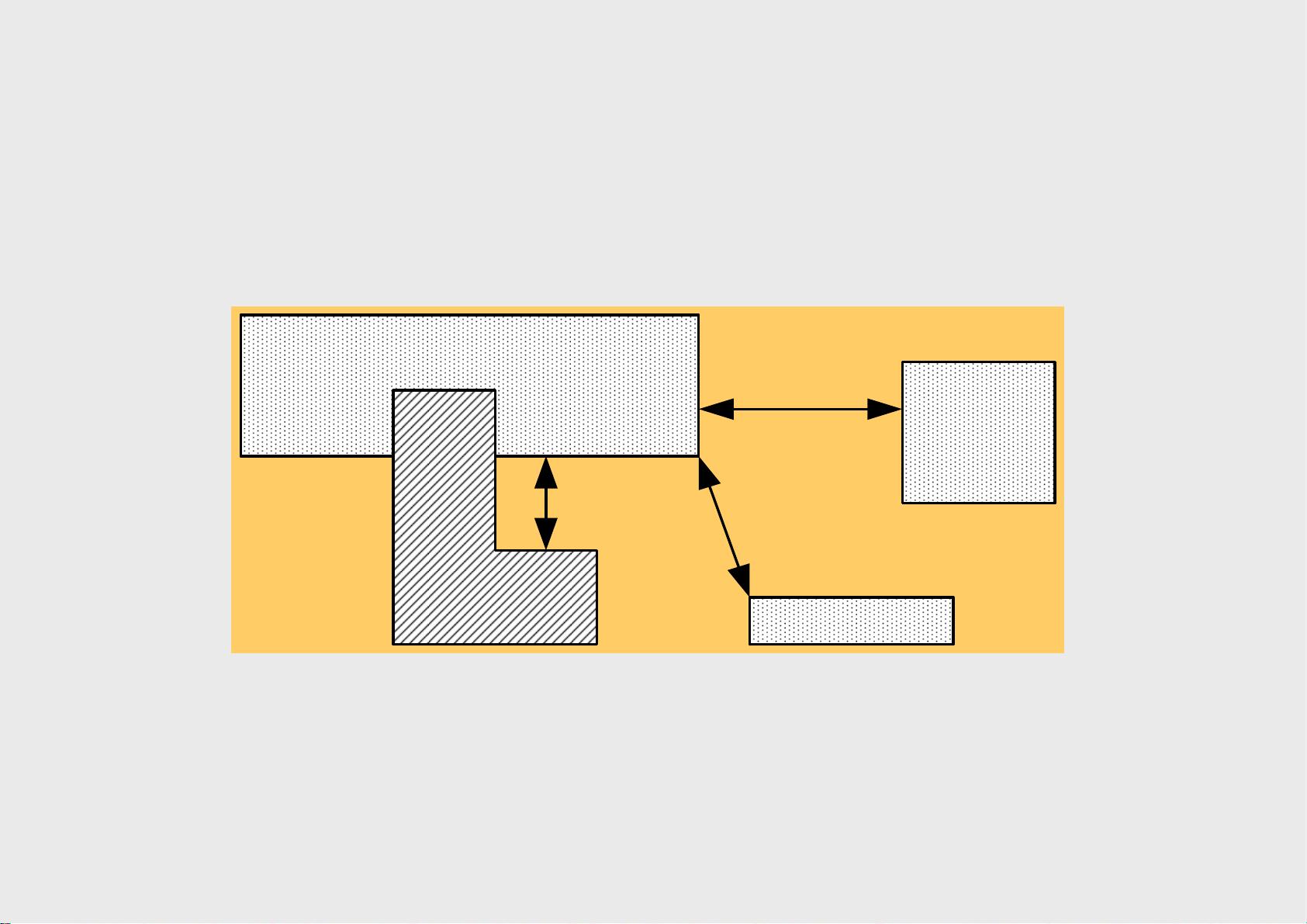

7. **芯片版图布局**:

版图布局涉及到整体芯片的组织,包括功能模块的定位、互连路径的选择以及封装接口的规划,以满足功能需求和面积效率。

8. **版图设计注意事项**:

设计过程中,设计者必须注意定期检查,防止错误积累,并充分考虑设计后期的验证和调试。同时,对设计规则的理解和遵守是提高设计质量的关键。

集成电路版图设计是一个系统性的过程,涵盖了工艺理解、规则遵循、工具应用和策略执行等多个层面,是芯片制造的基础和核心内容。

1204 浏览量

2009-03-22 上传

462 浏览量

150 浏览量

2009-10-02 上传

188 浏览量

379 浏览量

endkillerym

- 粉丝: 34

- 资源: 2

最新资源

- StudentManagement:JAVA+MySQL数据库设计完成的学生管理系统,界面使用的Java Swing

- 凡诺企业网站管理系统PHP版-PHP

- Unity独数游戏《sudoku-2017》

- Github-Trending-Repos-Android-App:一个基于Github api的Android应用,可根据创建日期显示趋势仓库

- 重量计算器

- lathe-firmware

- 2016 bctf exploit bcloud 400.rar

- 电脑软件一键禁用WIN10自带更新和杀毒.rar

- Auto Union Type.c Tab-crx插件

- ScreenToGif.2.17.1.Setup.msi

- easyapi:for面向人类的概念验证API生成器

- nodeDatagram

- angular-user-search-github::pencil_selector:简单的Angular-CLi应用程序搜索github用户

- jQuery基于CSS3文字动画特效特效代码

- omnetpp-5.5.1-src-windows.zip

- BabyShop:一个简单的电子商务网站,我们可以在其中租用一些婴儿用品。 有关更多信息,请浏览自述文件