DDR2-800与DDR3 PCB信号完整性和电源完整性设计策略

需积分: 10 144 浏览量

更新于2024-07-25

1

收藏 696KB PDF 举报

DDR2-800和DDR3的PCB信号完整性设计是一项关键任务,因为这两种内存标准在高速数据传输中对信号质量有严格要求。DDR2内存的速度可以达到800Mbps,甚至1066Mbps,而DDR3则可高达1600Mbps。在这样的速度下,PCB设计必须确保信号的时序匹配和波形完整性,以避免数据错误。

首先,PCB的叠层设计至关重要。在4层板限制下,信号通常在顶层和底层布线,中间层分别作为接地(GND)和平面电源(VDD)层。Vtt和Vref信号通常与VDD平面一起布设。增加到6层板后,电源和地层之间的距离减小,可以提升电源完整性(PI),使得信号传输更加稳定。

阻抗控制是另一个核心问题。在DDR2设计中,所有单端信号线需要保持50欧姆的连续阻抗,而差分信号线如CLOCK和DQS需要100欧姆的终端匹配。匹配电阻应上拉至VTT,并保持50欧姆。对于DDR3,ADDR/CMD/CNTRL等信号线上的单端匹配电阻可以选择40至60欧姆,这可以根据SI仿真结果进行微调。差分信号的阻抗匹配依然保持在100欧姆。

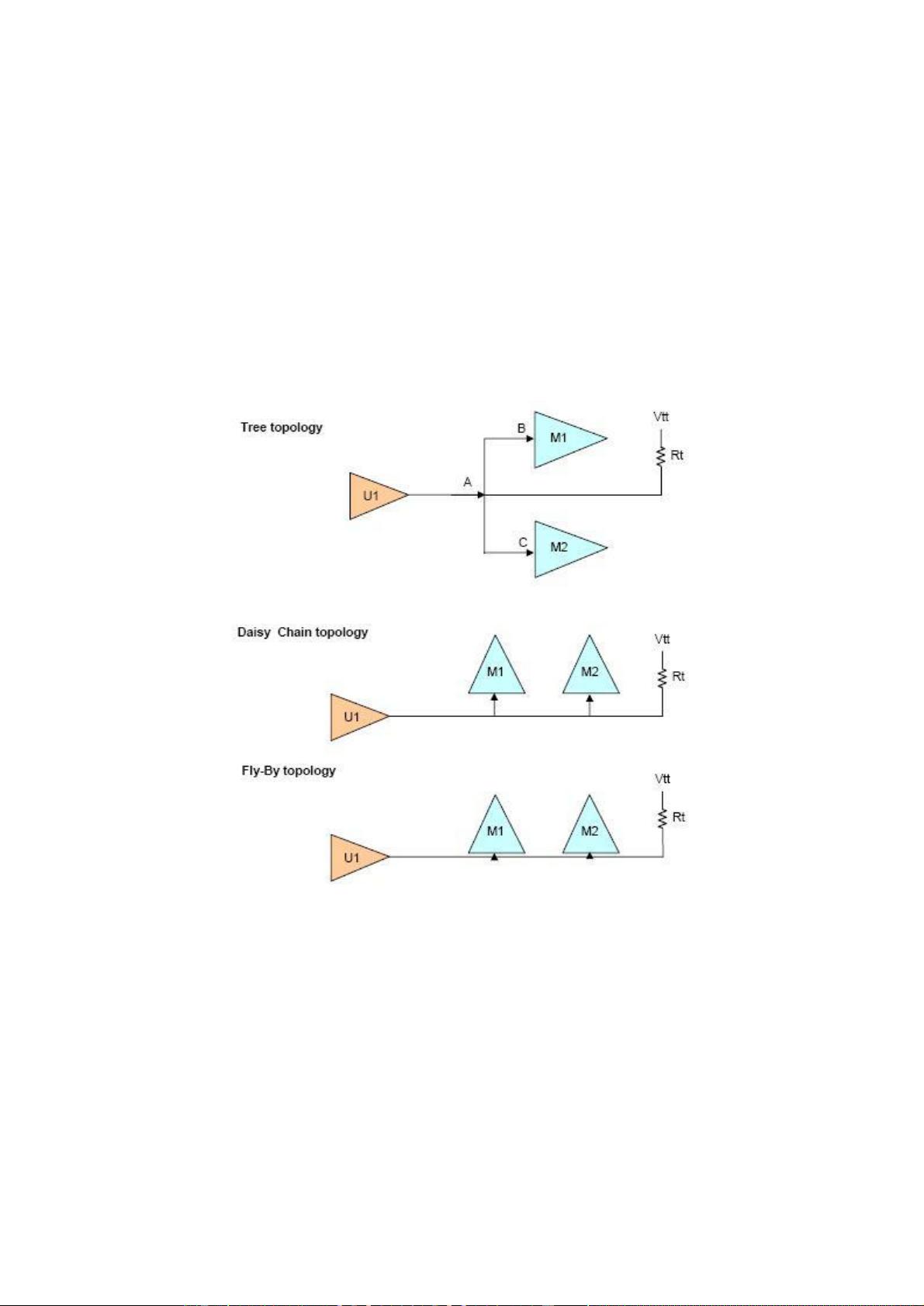

此外,时延匹配也是不可忽视的一环,确保数据在正确的时间到达接收端,以保证正确解码。串扰是高速信号传输中的常见问题,需要通过优化布线拓扑结构和间距来减少相邻信号间的干扰。例如,采用差分对信号可以有效降低串扰,因为它们在传输过程中产生的噪声相互抵消。

电源完整性方面,确保电源层和地层的布局合理,提供稳定的电压供应,减少噪声和波动,这对于高速数字电路来说至关重要。通常会使用电源分割和去耦电容来改善电源质量。

在设计过程中,EDA工具如Cadence Allegro SI-230和Ansoft's HFSS被广泛用于计算和仿真,帮助设计师优化信号完整性、电源完整性以及时序。通过这些工具,可以预估和解决潜在的问题,确保DDR2-800和DDR3系统在实际运行中的稳定性和可靠性。

DDR2-800和DDR3的PCB设计需要综合考虑多个因素,包括但不限于PCB叠层设计、阻抗控制、时序匹配、串扰管理和电源完整性优化。每个环节都需要精确计算和仿真,以实现高速、低误码率的数据传输。

128 浏览量

127 浏览量

265 浏览量

2024-11-05 上传

2024-11-05 上传

2024-11-05 上传

153 浏览量

2025-01-20 上传

2024-11-07 上传

torrestang

- 粉丝: 0

最新资源

- Visual Studio 2008:十大革新特性,包括LINQ和代码段编辑器

- CMPP2.0短信网关接口开发详解:协议结构与消息定义

- InfoQ出品:免费在线《深入浅出Struts2》教程

- Windows服务器2003数字证书与PKI实战指南

- C++TEST中文文档:代码标准分析和单元测试报告

- JS表单验证技巧集:字符限制、字符类型检测

- 一键式解决Java桌面应用的部署难题

- Android程序设计大赛I:20佳获奖作品展示与创新应用解析

- Oracle DBA基础教程:从开机到管理全记录

- 《人件》:软件工程中的人的因素与团队生产力

- 全球移动通信系统GSM:原理与频段解析

- 《Linux内核0.11完全注释》:深入理解操作系统核心

- 浅析计算机键盘构造与PS/2接口原理详解

- SIMATIC S7-300编程手册:STL指令详解

- Visual Source Safe (VSS) 在软件开发中的应用

- Java命令参数详解:从基础到扩展