TI TPS74401电源芯片详细教程:0.8V-3.6V低dropout线性稳压器

需积分: 49 131 浏览量

更新于2024-07-04

收藏 411KB PDF 举报

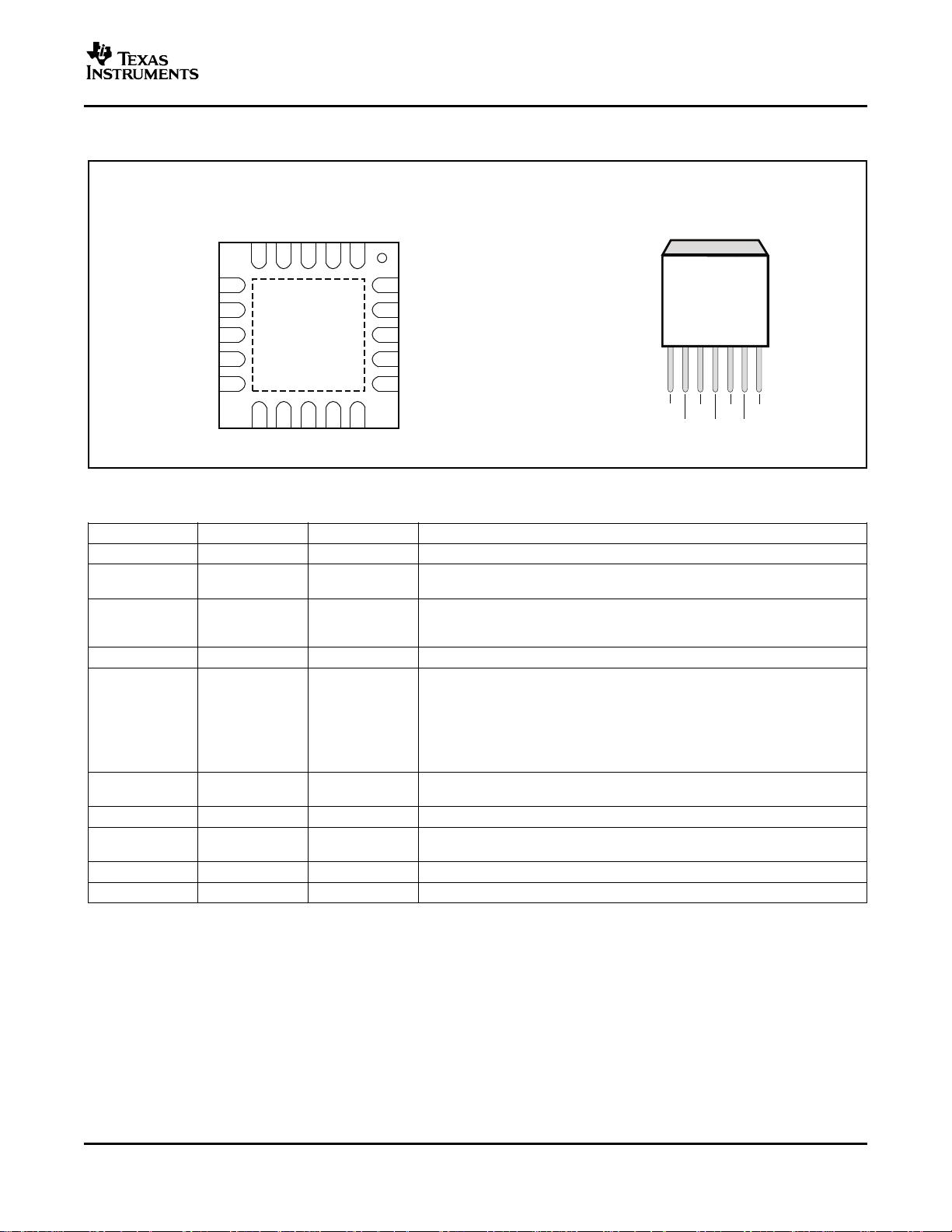

本文档是德州仪器(TI)公司的一款高性能电源管理芯片TPS74401的使用说明书。该芯片是一款超低降压线性稳压器,专为各种应用设计,特别是那些对电源效率、稳定性及启动特性有高要求的系统。TPS74401的主要特点包括:

1. **宽广的电压调节范围**:输出电压可以在0.8V至3.6V之间灵活调整,满足不同设备对于电压的需求,特别适用于ASICs(应用特定集成电路)和处理器等电子元件。

2. **软启动功能(SS Pin)**:通过外部电容器设置的上拉时间,TPS74401的软启动机制允许用户轻松控制启动过程,减少对输入电源的冲击,并降低启动时的电流消耗,确保了系统的稳健启动。

3. **1%精度**:在负载和工作线路上,该稳压器具有出色的精度,确保输出电压稳定,适应性强,即便在极端条件下也能提供准确的电压控制。

4. **低电压输入兼容**:支持最低0.9V的输入电压,这使得该芯片能够应用于电压较低的电源环境中,减少了启动时的电容性负载电流,提升了整体效率。

5. **外部偏置供电**:除了标准的供电接口外,TPS74401还支持外部偏置供电,这增加了设计灵活性,可以根据需要调整电路配置。

6. **可编程软启动时间**:用户可以根据具体应用需求,调整软启动时间,以优化设备的上电过程,减少对电路的影响。

7. **易于序列化操作**:通过enable输入和power-good输出,设计师可以轻松实现多个TPS74401器件的顺序控制,便于系统级集成。

8. **极低的降压损耗**:在典型条件下,当输出电流为3.0A时,降压损耗仅为115mV,显示出其高效能的特点。

9. **稳定性保障**:无论负载如何变化,TPS74401都能保持输出电压的稳定,这对于需要精确电压控制的微电子设备至关重要。

TPS74401是一款针对低功耗、高性能电子系统设计的理想选择,尤其适合那些对启动性能、电压准确性、以及电源管理有着严格要求的应用场景。设计师在使用时,需要根据手册中的参数和电路图示例,正确配置外部元件如电阻(R1、R2、R3)和电容(COUT、CIN),以达到最佳性能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

804 浏览量

317 浏览量

140 浏览量

193 浏览量

184 浏览量

378 浏览量

月半不知愁

- 粉丝: 1

- 资源: 6

最新资源

- p3270:一个用于控制远程IBM主机的python库

- magic-iswbm-com-zh-latest.zip

- deeplearning-js:JavaScript中的深度学习框架

- 易语言控制台时钟源码.zip

- 完整的AXURE原型系列1-6季的全部作品rp源文件

- RC4-Cipher:CSharp中的RC4算法

- 测试

- 威客互动主机管理系统 v1.3.0.5

- metrics-js:一个向Graphite等聚合器提供数据点信息(度量和时间序列)的报告框架

- Kubernetes的声明式连续部署。-Golang开发

- IsEarthStillWarming.com::fire:全球变暖信息和数据

- Ajedrez-开源

- 社区:Rust社区的临时在线聚会。 欢迎所有人! :globe_showing_Americas::rainbow::victory_hand:

- Algo-ScriptML:Scratch的机器学习算法脚本。 机器学习模型和算法的实现只使用NumPy,重点是可访问性。 旨在涵盖从基础到高级的所有内容

- 支持Google的协议缓冲区-Golang开发

- 手写体数字识别界面程序.rar_图片数字识别_手写数字识别_手写识别_模糊识别_识别图片数字