FPGA实现插值滤波技术详解

需积分: 0 184 浏览量

更新于2024-08-05

2

收藏 1.02MB PDF 举报

"插值代码分析1"

本文主要探讨了FPGA实现的插值滤波技术,涵盖了实现要求、插值滤波原理以及FPGA实现流程,并进行了模块分析。

一、实现要求

在FPGA开发中,插值滤波器需要满足特定的功能要求。它应能实现对信号的2、5、10、20、25、50、100倍插值。滤波器的系数需从外部输入并存储在内部RAM中。关键的外部输入参数包括312.5MHz的时钟(用于插值模块),100MHz的时钟(用于系数存储),以及来自前级模块的待插值信号、FIFO满信号、输入有效信号、复位信号、使能信号和清零信号。此外,插值倍数和滤波器系数由PC机通过特定地址发送。输入时序要求严格的同步操作,如先复位,然后发送地址和系数,最后在满足特定条件后输入插值信号。

二、插值滤波原理

插值滤波是提高信号抽样率的技术,通过对原始信号在每个采样点之间插入零点来实现。以3倍插值为例,原始信号每两个点之间插入两个零点。在频域中,插值等同于对信号的傅里叶变换进行伸缩,即将频谱压缩L倍。这会导致原频谱的副本在更高频率处出现,形成L-1个镜像。为了消除这些镜像,通常需要设计适当的滤波器来避免失真。

三、FPGA实现流程

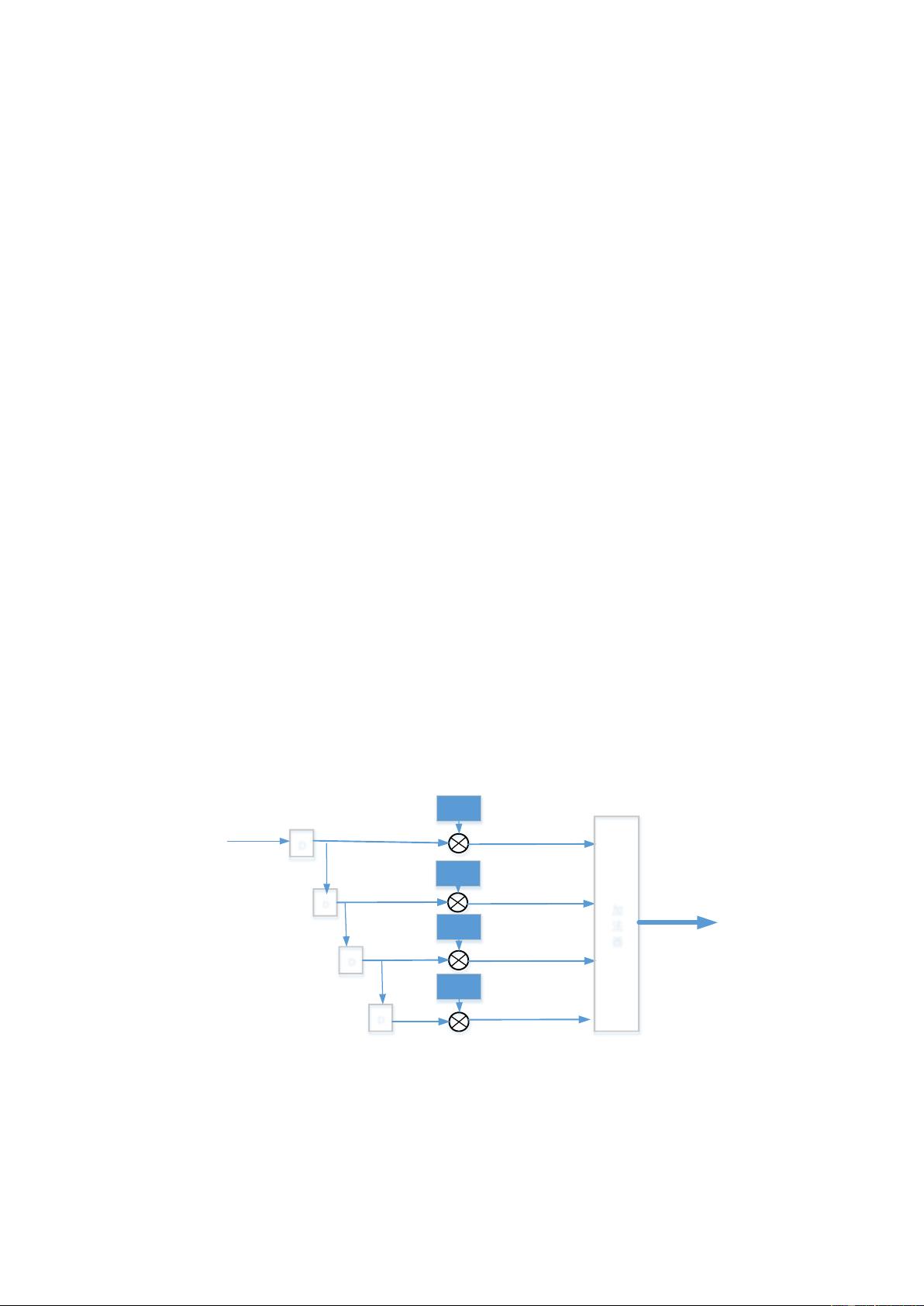

在FPGA中实现插值滤波,首先需要设计一个能够处理外部输入信号和控制信号的接口模块。然后,构建一个系数RAM模块,用于存储从外部输入的滤波器系数。接下来,实现一个插值引擎,它根据输入的插值倍数决定如何插入零点。插值引擎可能包含一个分频器来调整内部采样率。接着,设计一个滤波器模块,该模块基于所存储的系数进行滤波操作,消除镜像。最后,需要一个输出控制器,它根据输入有效信号和FIFO的状态将处理后的信号发送出去。

四、模块分析

1. 接口模块:负责接收和解析来自前级模块和PC机的信号,如地址、系数、复位和使能信号。

2. 系数RAM模块:存储滤波器系数,支持快速读取。

3. 插值引擎:根据插值倍数调整输入信号,插入零点。

4. 滤波器模块:设计合适的数字滤波算法(如FIR或IIR滤波器)来消除插值产生的镜像。

5. 输出控制器:控制信号的正确输出,确保与外部系统的同步。

FPGA实现的插值滤波涉及到硬件描述语言编程,信号处理理论,以及高速数字信号处理的设计技巧。每个模块的设计和优化对于整个系统性能至关重要,尤其是在实时性和带宽要求较高的应用中。

2021-02-14 上传

2009-10-30 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2015-08-27 上传

2017-03-04 上传

2018-04-07 上传

2023-03-07 上传

亚赛大人

- 粉丝: 34

- 资源: 332

最新资源

- 图书管理系统概要设计说明书

- 图书管管理系统项目开发计划书

- 入门教程 CSS属性.pdf

- Beginning_Linux_Programming_Third_Edition

- Cloud Computing and Grid Computing 360-Degree Compared

- 基于J2EE的Ajax宝典

- 德州大学AMOS教程(中文)

- 跟我一起写makefile

- websvcs-1_2-fr.pdf

- 搜索引擎优化知识完全手册

- 实战 XML.pdf

- Visual Basic 2005 基础教程

- oracle使用初级教程

- eclipseCvs

- 将Java项目打包成可执行文件.pdf

- 西瓜外语通制作英语词汇同步MP3操作指南