Xilinx FPGA IBIS模型定制与生成教程:专家老胡的实践分享

需积分: 10 144 浏览量

更新于2024-08-26

收藏 743KB DOCX 举报

本文主要探讨了Xilinx FPGA的模型分配流程,特别是针对IBIS模型在信号完整性仿真的重要性及其挑战。Xilinx提供的通用IBIS模型可能并不适用于所有特定应用,因为FPGA的实际使用中,管脚映射会根据具体设计有所变化。这些预设的模型可能包含了未被实际硬件使用的管脚,导致在仿真时出现找不到管脚的错误。

文章首先指出了问题的根源,即每个FPGA项目都需要根据实际的管脚配置进行定制化的IBIS模型生成,而Xilinx官方模型并未考虑到这种多样性。作者提供了两种解决方案:一是利用Vivado的内置功能,通过输入与PCB一致的管脚分配文件自动创建模型;二是手工编辑生成模型,这需要对IBIS文件的语法有一定了解。

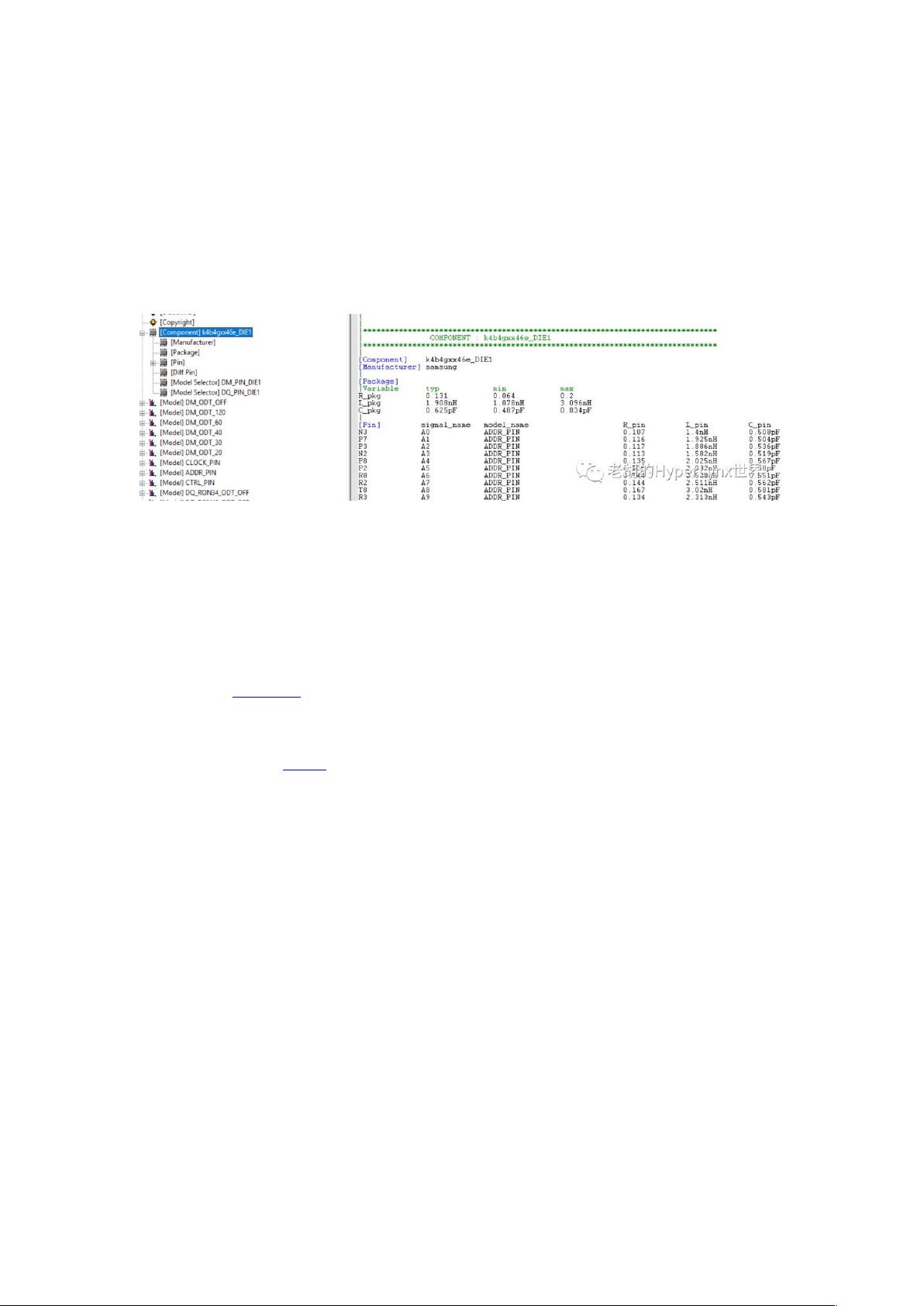

在手工生成FPGA IBIS模型时,作者详细介绍了IBIS文件的基本结构,包括文件头(版本和制造商信息)、元件定义、封装参数的三种定义方式(全局封装参数、单个管脚参数和封装模型引用)、管脚映射关系的[Pin]段、以及可能需要多个模型描述的[ModelSelector]段。特别强调了[Pin]段的重要性,它是编辑的核心,用于指定每个管脚与其IBIS Buffer模型的对应关系,并设置寄生参数。

对于初学者或不熟悉IBIS语法的人来说,手工编辑可能会更具挑战性,但掌握这项技能对于确保模型的精确性和仿真结果的准确性至关重要。因此,本文不仅提供了实用的工具和技术,还强调了理解和掌握IBIS模型生成技巧在现代FPGA设计中的必要性,无论是自动还是手动,都能帮助设计师优化信号完整性并提升仿真效率。

2022-10-28 上传

2022-04-14 上传

285 浏览量

148 浏览量

142 浏览量

224 浏览量

103 浏览量

2021-11-10 上传

2022-06-02 上传

知寒xx

- 粉丝: 10

- 资源: 13

最新资源

- 用敏捷方法实施基于CMM的软件过程改进

- 高质量C++/C 编程指南

- Intel32位编程手册,卷三

- 2008年4月全国计算机等级考试四级软件测试工程师笔试真题(非图片版)

- Intel32位编程手册,卷二

- Pro.EJB.3.Java.Persistence.API.pdf

- Delphi7下IntraWeb应用开发详解.pdf

- PC8TBD_Student_Guide.pdf

- Intel32位编程手册 ,卷一

- C#学习手册,基础的东西,适合新手

- 粗糙集属性约减c++源代码

- 初步了解JDBC入门必看

- 人工智能论文.doc

- oracle 2日速成

- USB 2.0协议层规范分析

- java面试题经典(全面)