Verilog HDL入门:全加器到补码加减法运算器设计

需积分: 17 74 浏览量

更新于2024-07-15

1

收藏 1.05MB DOC 举报

"这篇文档是关于Verilog HDL的学习指南,特别针对计算机组成原理课程设计中的加法器和减法器设计。通过一系列的实践关卡,学生将掌握Verilog HDL的基础,包括全加器、无符号二进制加法器、减法器以及定点二进制数的补码加减法运算器的设计。"

在计算机科学领域,Verilog HDL(硬件描述语言)是一种被广泛用于数字电子系统设计的语言,特别是集成电路和 FPGA(现场可编程门阵列)设计。这篇文档名为“Verilog初体验”,是针对计算机组成原理课程设计的一个实践项目,旨在帮助学习者入门Verilog HDL,并通过实际操作加深对加法器和减法器等基本计算单元的理解。

实习内容包括四个主要部分:

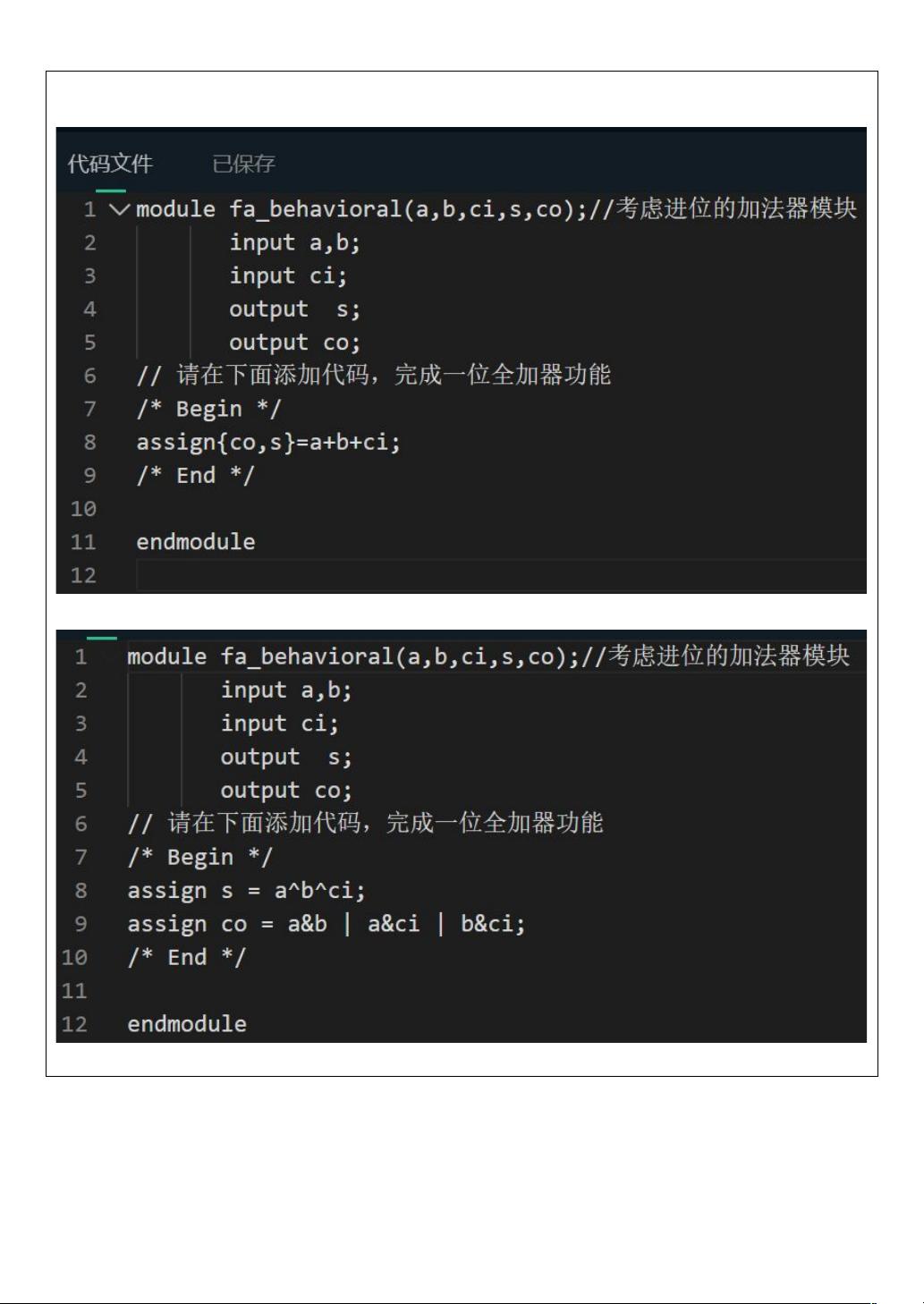

1. **全加器设计**:全加器是数字电路中处理二进制加法的基本组件,它不仅考虑了当前位的加法,还处理了进位。全加器的真值表展示了所有可能的输入和输出状态,通过布尔代数可以推导出其逻辑表达式,并最终实现为逻辑电路。

2. **无符号二进制数加法器**:无符号二进制加法器处理的数没有正负之分,只进行单纯的数值相加。设计这样的加法器,需要理解二进制数的运算法则,并能够用Verilog HDL描述这些规则。

3. **减法运算器**:减法器是基于加法器原理构建的,通常通过二进制补码表示负数来实现减法。减法器需要处理借位的情况,对于无符号数,减法等同于加法的补码。

4. **定点二进制数的补码加减法运算器**:定点数是指小数点位置固定的二进制数,补码表示法用于处理负数。补码加减法运算器需要处理正负数的加减,涉及符号位的处理和溢出检测。

实习过程中,学生按照时间线进行,从确定设计任务、查阅资料开始,到画出原理图,然后不断优化设计方案,最后完成设计并进行验证。这个过程有助于学生掌握Verilog HDL的基本语法和设计流程,同时也对数字逻辑电路有更深入的理解。

通过这种实践性的学习,学生不仅能学会如何用Verilog HDL编写代码来描述数字逻辑,还能了解这些基本运算单元在实际计算机系统中的应用。这将为他们未来深入学习计算机体系结构和其他高级数字系统设计打下坚实基础。

2021-02-03 上传

2013-06-21 上传

2024-01-20 上传

2023-09-14 上传

2023-10-15 上传

2023-08-19 上传

2023-05-11 上传

2023-05-11 上传

Fanknowledge

- 粉丝: 1

- 资源: 6

最新资源

- MATLAB实现小波阈值去噪:Visushrink硬软算法对比

- 易语言实现画板图像缩放功能教程

- 大模型推荐系统: 优化算法与模型压缩技术

- Stancy: 静态文件驱动的简单RESTful API与前端框架集成

- 掌握Java全文搜索:深入Apache Lucene开源系统

- 19计应19田超的Python7-1试题整理

- 易语言实现多线程网络时间同步源码解析

- 人工智能大模型学习与实践指南

- 掌握Markdown:从基础到高级技巧解析

- JS-PizzaStore: JS应用程序模拟披萨递送服务

- CAMV开源XML编辑器:编辑、验证、设计及架构工具集

- 医学免疫学情景化自动生成考题系统

- 易语言实现多语言界面编程教程

- MATLAB实现16种回归算法在数据挖掘中的应用

- ***内容构建指南:深入HTML与LaTeX

- Python实现维基百科“历史上的今天”数据抓取教程