DM9302:10/100Mbps光纤/双绞线转换器详解

需积分: 10 93 浏览量

更新于2024-09-09

收藏 346KB PDF 举报

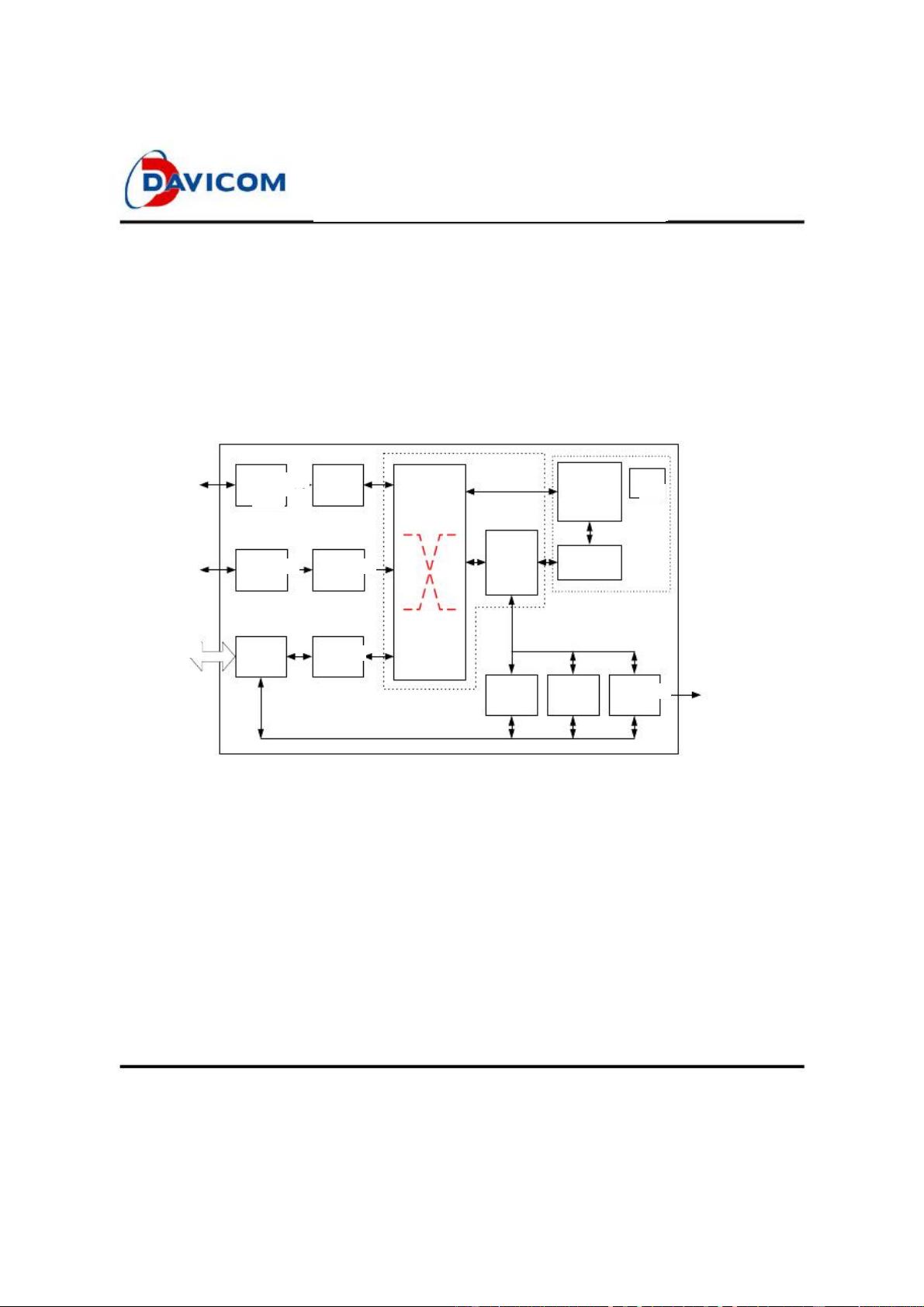

DM9302是一款10/100Mbps以太网光纤/双绞线收发器,它是一个单芯片解决方案,旨在实现IEEE802.3标准下的100BASE-TX(铜缆)和100BASE-FX(光纤)信号间的转换,适用于快速以太网通信。这款转换器主要应用于需要在光纤和双绞线介质之间进行连接的场景,如连接光纤网络段、延长距离或连接不同的网络设备,以提供灵活的互连方式。

该收发器的关键特性包括:

1. **单芯片设计**:DM9302采用集成的10/100BASE-TX/FX开关,简化了硬件结构,提高了效率。

2. **标准兼容性**:它符合IEEE802.3u标准,支持100BASE-TX,并遵循ANSI X3T12 TP-PMD和X3.166 FDDI-PMD标准。

3. **处理能力**:拥有8位/16位处理器接口,支持4个优先级队列,包括基于端口的VLAN(Virtual Local Area Network)支持和802.1Q VLAN上行功能,以及VLAN ID标记/取消标记选项。

4. **带宽管理**:每个端口支持入口和出口速率控制,具备广播风暴过滤功能,支持存储转发交换和流量控制机制,包括全双工模式下的IEEE802.3x和半双工模式下的背压控制。

5. **MAC地址处理**:支持1K单播MAC地址的重新编码和自动老化策略,确保高效的数据包处理。

6. **配置方式**:通过EEPROM接口实现上电配置,提供MIB-II管理功能,便于系统监控和调试。

7. **接口兼容性**:兼容3.3V和5.0V宽容的I/O,支持DSPPHY和HPAuto-MDIX,采用64引脚LQFP封装,采用0.18微米工艺,符合RoHS无铅和无卤素环保要求。

8. **物理层特性**:DSPPHY设计,支持自动检测并切换MDI/MDIX模式,确保连接的灵活性。

DM9302是一款功能强大的媒体转换器,适合于需要灵活连接不同网络介质的场合,通过其丰富的特性提供了高效、可靠和可管理的网络连接解决方案。

575 浏览量

2015-06-03 上传

2015-06-03 上传

2015-06-03 上传

点击了解资源详情

2021-10-01 上传

115 浏览量

CharMingSly

- 粉丝: 2

- 资源: 14

最新资源

- vip会员统计表excel模版下载

- containerBooking

- like-me

- node-async-await-example:具有异步等待用法的Node.js应用程序的简单示例

- F460dll_for_TOT_KLS.rar

- NRRD 格式文件阅读器:NRRD 文件阅读器-matlab开发

- upptime:Up Upptime的正常运行时间监视器和状态页面,由@upptime提供支持

- 幼儿园财务报表excel模版下载

- Calculator:在Android Studio上使用Kotlin的基本计算器

- luckytuan-fast-loader-master.zip

- adc-analysis:SciCRT的跟踪分析

- SCANProject:堆叠式交叉注意项目页面

- 公司会议室3D模型

- pushNaNs:将 NaN 推送到 X 的每一列的底部。-matlab开发

- ManuelGil:个人资料

- 爱普生(Epson)L805 原版清零软件