Vivado实现与静态时序分析详解

需积分: 6 75 浏览量

更新于2024-07-17

收藏 1.34MB PPTX 举报

"这篇文档是关于Xilinx FPGA设计流程中的Implementation(实现)和Static Timing Analysis(静态时序分析)的教程,主要针对Vivado 2013.4版本。文档旨在帮助读者理解从综合后的代码到最终比特流生成的整个过程,以及如何进行有效的静态时序分析和硬件验证。"

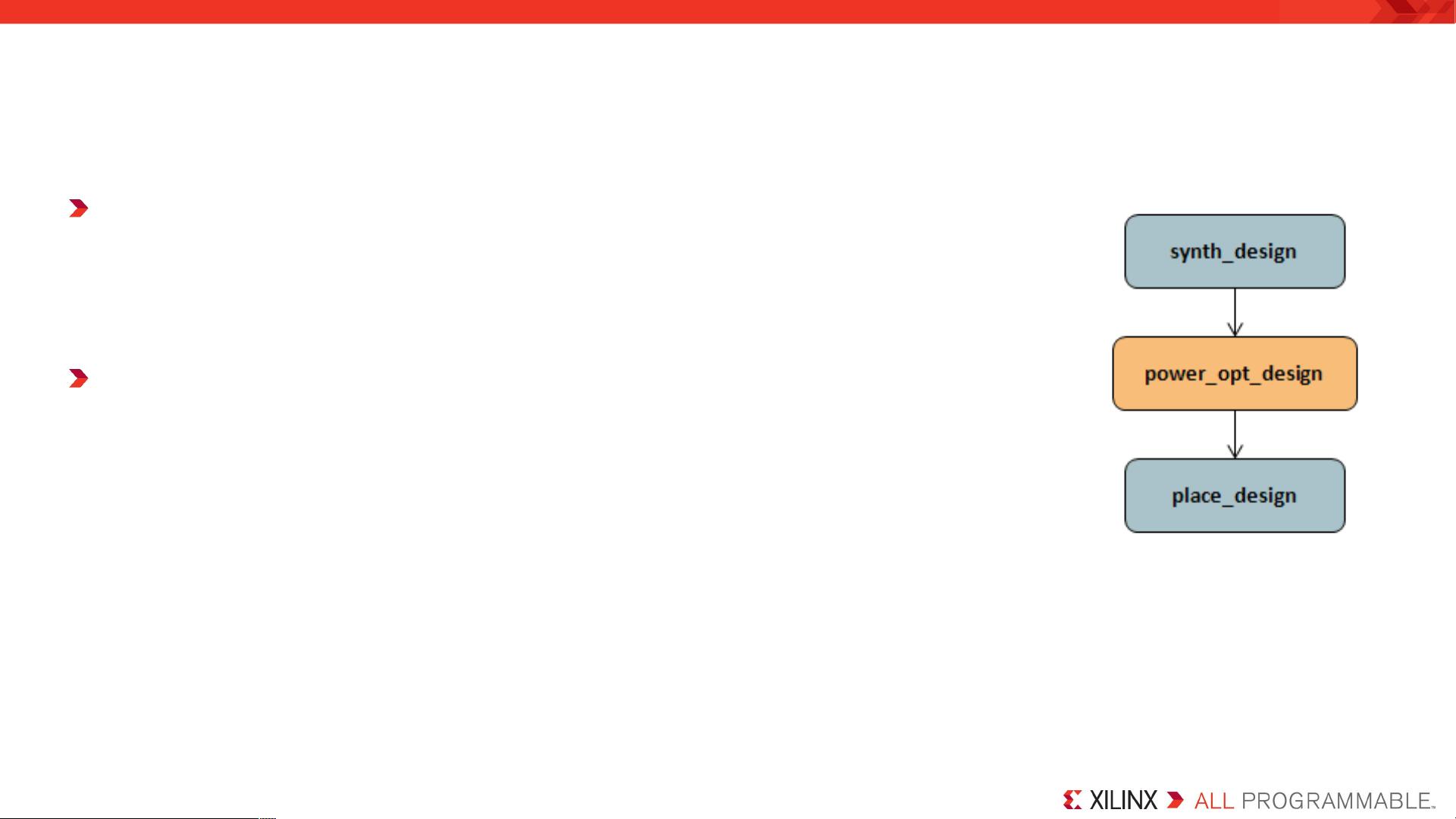

在Xilinx FPGA设计中,Implementation是一个关键步骤,它涵盖了从逻辑综合后的网表到物理布局布线的全过程。这个阶段的目标是将逻辑设计转化为可以在FPGA硬件上执行的配置数据,即比特流(bitstream)。在Vivado工具中,Implementation包括了多个子步骤,如逻辑优化、映射、时钟树合成、布线等,确保设计能够在目标器件上以最佳性能运行。

1. **Implementation Reports**:在实施过程中,Vivado会生成多种报告,如功耗报告、面积报告、时序报告等,这些报告提供了设计实现后的详细信息,有助于优化设计并检查潜在问题。

2. **Static Timing Analysis (STA)**:是FPGA设计中不可或缺的一环,用于评估设计是否满足时序要求。它通过分析设计中的静态时序路径(即在所有可能输入组合下时延固定的路径),确定关键路径,确保设计满足建立时间(setup time)和保持时间(hold time)的要求。

3. **Setup and Hold Checks**:建立时间和保持时间是时序分析的核心概念。建立时间是指数据必须在时钟边沿之前到达触发器,以保证正确捕获;保持时间是指数据在时钟边沿之后必须保持稳定的时间,以避免数据在触发器内部被错误读取。

4. **Clocks and Timing Checks**:时钟与建立保持检查的关系密切,不同的时钟域可能导致复杂的时序问题。理解和管理时钟关系是确保设计时序闭合的关键。

5. **Custom Timing Reports**:用户可以自定义时序报告,以关注特定的路径或设计区域,这在解决时序问题或优化性能时非常有用。

6. **Timing Summary Report**:此报告汇总了设计的总体时序性能,包括满足和未满足的约束,是验证时序约束是否得到满足的主要依据。

7. **Bitstream Generation**:在完成所有的设计优化和时序分析后,Vivado会产生一个比特流文件,该文件包含了配置FPGA所需的全部信息。这个比特流可以下载到FPGA中,使设计在硬件上运行。

8. **Hardware Verification**:最后,生成的比特流需要在实际硬件上验证,确保设计的功能正确性和满足的时序要求。

本教程涵盖了从基本的时序分析到比特流生成和硬件验证的整个流程,对理解和优化Xilinx FPGA设计的实现阶段具有重要指导价值。通过学习,设计者能更好地理解和处理设计实现中的各种挑战,从而提高设计的效率和可靠性。

136 浏览量

131 浏览量

2025-02-16 上传

2025-02-16 上传

2025-02-16 上传

YanJ000

- 粉丝: 0

最新资源

- HTML教程:实现海绵宝宝案例式文本转换

- Tableau中缺失日期的快速填补解决方案

- ASP多媒体课程答疑系统:源代码与论文详解

- 声音报警系统设计与仿真实验教程

- 易语言菜单操作教程:基础例程解析

- WPF中控件拖动与尺寸自定义的实现方法

- Delphi实现窗体句柄遍历的截图工具方法

- 掌握MATLAB同态滤波技术,提升图像处理效果

- 第2周挑战赛决赛揭幕:技术与策略的较量

- HTML5蓝色拼图游戏实现与源码解析

- STM32工程模板:IAR集成UCOS-III源码

- ASP+ACCESS学生成绩查询系统毕业设计全套资料

- 使用Pygame制作动态主角及移动效果

- Spring Boot与Vue打造家庭食谱管理平台

- 易语言实现超级编辑框文本搜索选中功能

- 智能手机应用前端模板:HTML5与CSS3的完美结合