2010年SpectreRF指南:噪声感知PLL设计流程详解

需积分: 10 124 浏览量

更新于2024-07-20

收藏 3.72MB PDF 举报

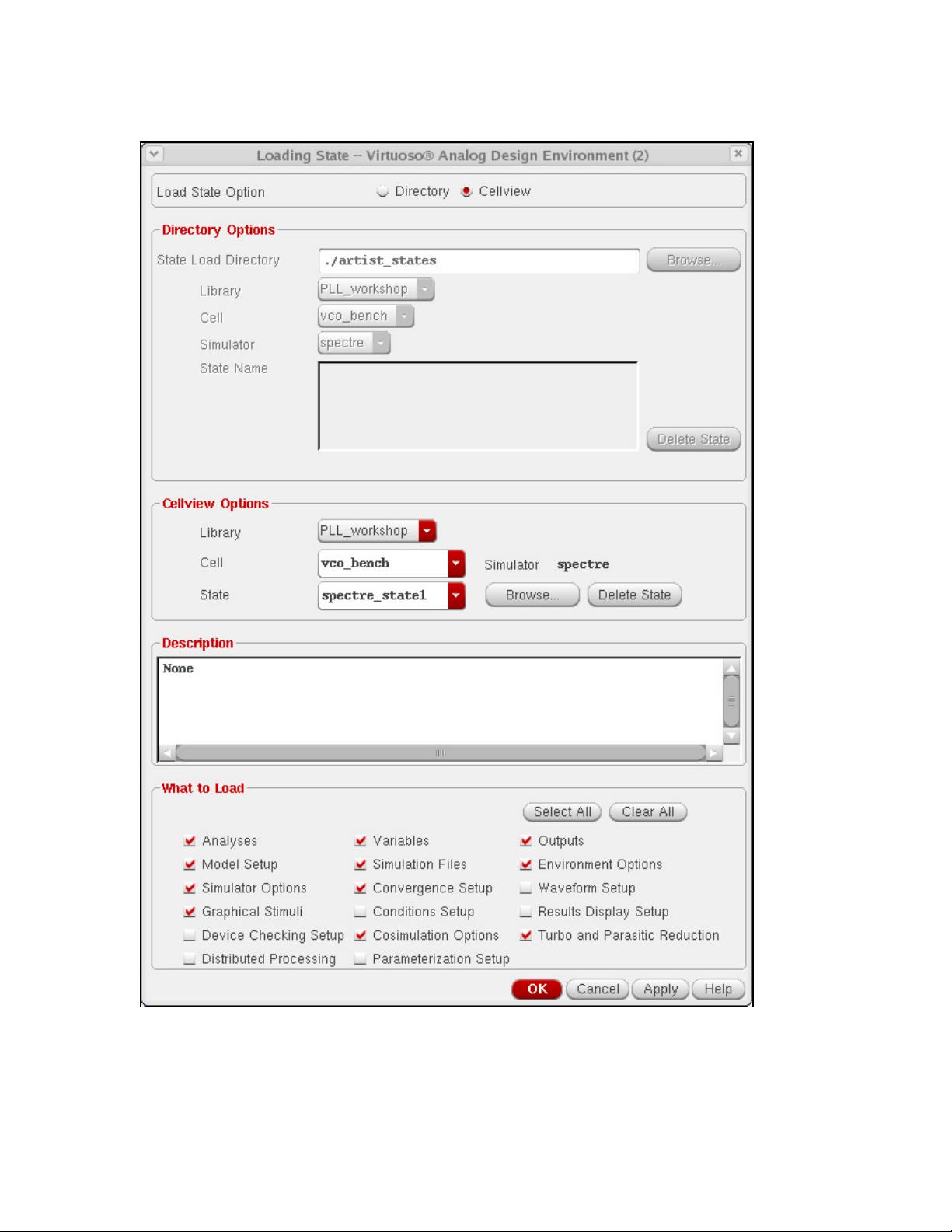

"Noise Aware PLL Design Flow是一份详细的指南,针对在设计锁相环/频率综合器时如何处理噪声问题。这本书籍或教程于2010年发布,使用的是Spectre RF Workshop和MMSIM 7.2.0版本。该设计流程旨在帮助工程师们创建高性能、抗干扰的PLL系统,这些系统广泛应用于时钟同步、频率合成以及数据恢复等领域,其中关键性能指标之一就是对输入噪声的抑制能力。

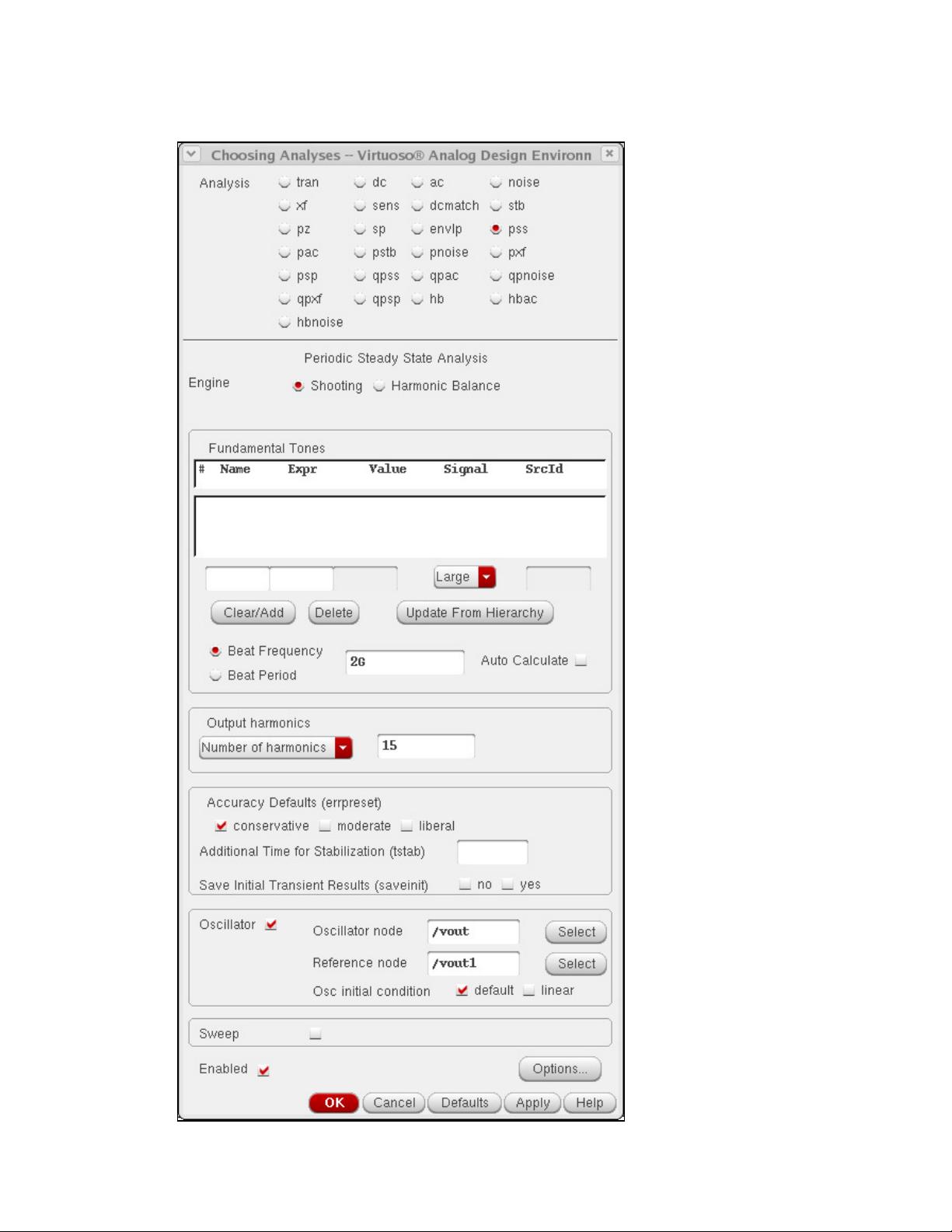

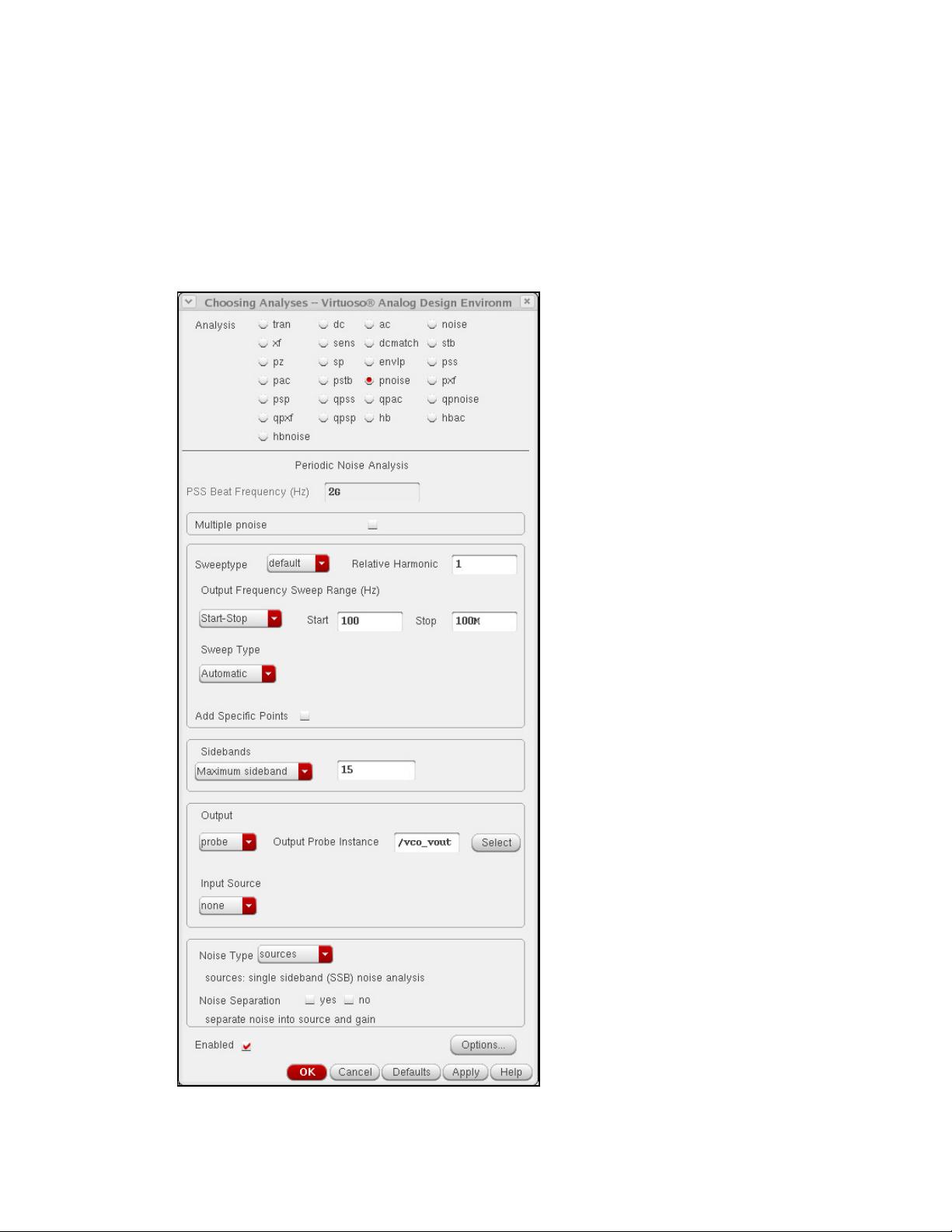

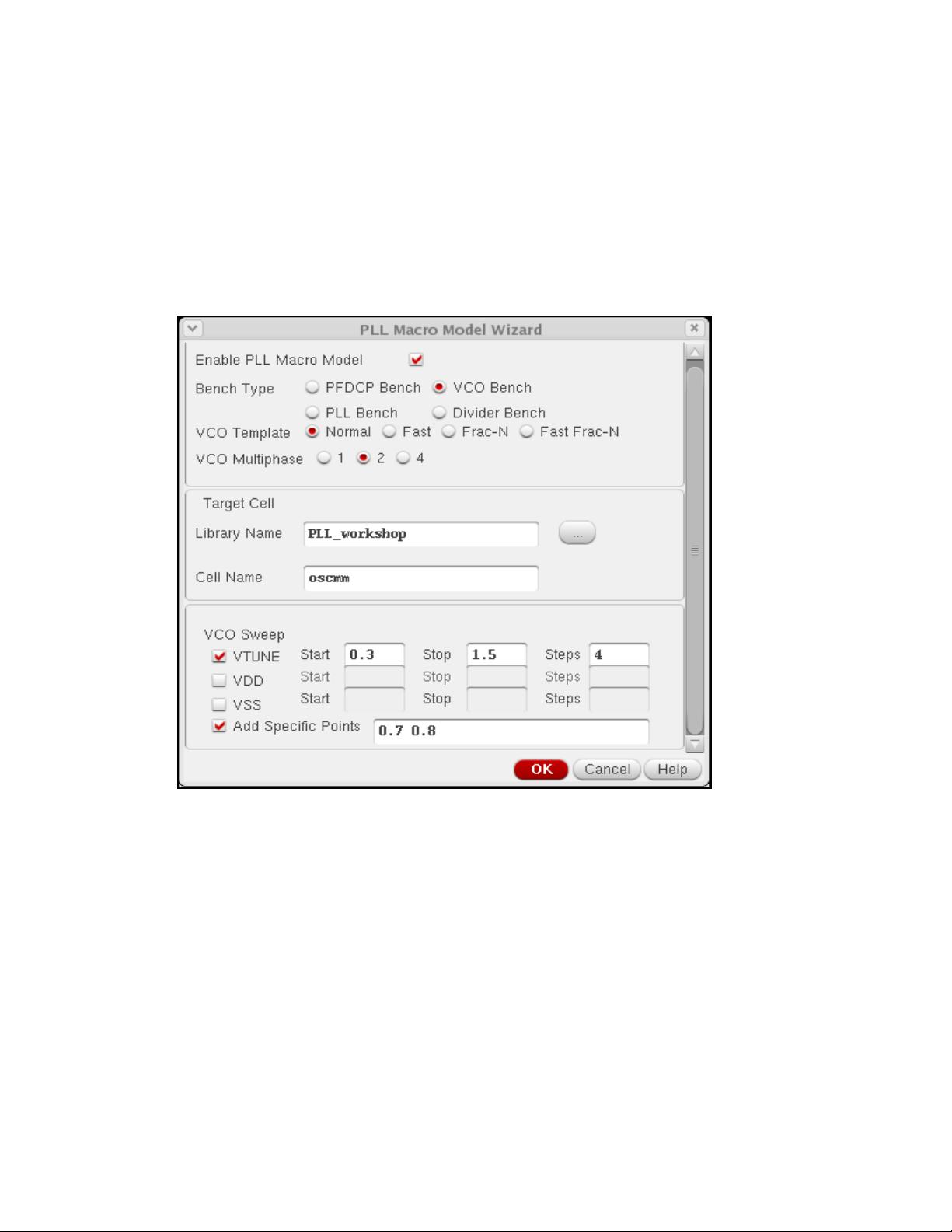

设计流程分为两部分:整数N PLL设计和分数N PLL设计。首先,介绍部分概述了PLL的基本原理,指出PLL用于实现频率锁定和时钟稳定,任何来自VCO(电压控制振荡器)或PFD(相位分频器)的抖动或相位噪声都可能影响输出质量。因此,了解和管理噪声是设计过程中的重要环节。

在整数N PLL设计部分,指导读者如何下载和使用GPDK 180.6工具包,这包括建立一个CMOS模型来模拟VCO/Divider(即VCO和分频器),这两个组件通常是PLL的核心。接着,用户被引导创建PFD/CP(相位检测器和控制寄存器)的模型,这是PLL中用于比较输入信号与参考信号并进行相位调整的关键部分。

对于分数N PLL设计,流程保持相似,但重点在于更精细的频率调整。同样,先创建VCO/Divider模型,然后构建PFD/CP模型。这一阶段的特色在于可以实现更灵活的频率合成,但同时也需要处理更多的噪声源。作者还建议可选地创建分频器的模型,以进一步优化系统性能。

整个流程不仅涉及理论概念,还包含模拟步骤,如如何通过仿真模拟分数N PLL的行为,以评估其在实际应用中的噪声敏感性。最后,书中附有常见问题解答(FAQs),解答在噪声感知PLL设计过程中可能会遇到的技术难题。

Noise Aware PLL Design Flow提供了一个实用且系统化的步骤,帮助工程师们在面临噪声挑战时,能够设计出更为稳健、高效的锁相环,确保系统在高精度时钟同步和信号处理任务中表现出色。"

2013-07-08 上传

2021-02-07 上传

2021-02-09 上传

2021-02-08 上传

2021-02-09 上传

105 浏览量

2021-02-22 上传

130 浏览量

2021-02-11 上传

xxgenerall

- 粉丝: 0

- 资源: 8

最新资源

- FonePaw_Video_Converter_Ultimate_2.9.0.93447.zip

- 162100头像截图程序 4.1

- subclass-dance-party

- JavaScript:Curso完成JavaScript

- Medical_Payment_Classification:确定医疗付款是用于研究目的还是用于一般用途

- P1

- javascript-koans

- 保险行业培训资料:寿险意义与功用完整版本

- ChandyMishraHaasOrAlgo

- maven-repo

- react-as-space

- eclipse-inst-mac64.dmg.zip

- bearsunday.github.io

- ks

- lazytoby.github.io

- 0.96寸OLED(IIC接口)显示屏的图像显示应用