Vivado仿真实战:验证电路功能与优化流程

需积分: 0 128 浏览量

更新于2024-08-05

收藏 895KB PDF 举报

实验05主要探讨在Vivado环境中使用Verilog进行电路设计和仿真的过程。该实验旨在帮助学生熟悉Vivado软件的下载、安装及使用,提升他们编写和验证电路功能的能力。

首先,电路描述部分强调了Verilog的重要性,它是硬件描述语言(HDL),常用于FPGA和ASIC的设计。在电路实现阶段,通过Verilog代码来定义电路的逻辑结构,包括逻辑门、触发器、模块等。Vivado作为Xilinx的集成开发环境,提供了全面的功能,如设计输入、综合、仿真和编程下载等。

电路运行在FPGA实验平台上时,由于Vivado的综合速度较慢且无法实时定位问题,所以实验建议先使用Vivado的仿真功能进行验证。在Logisim中,验证过程包括绘制电路、设置输入值和观察输出信号的状态,而在Vivado中则涉及到创建Verilog仿真文件,通过波形分析检查电路行为是否符合预期。

实验目的明确,包括:

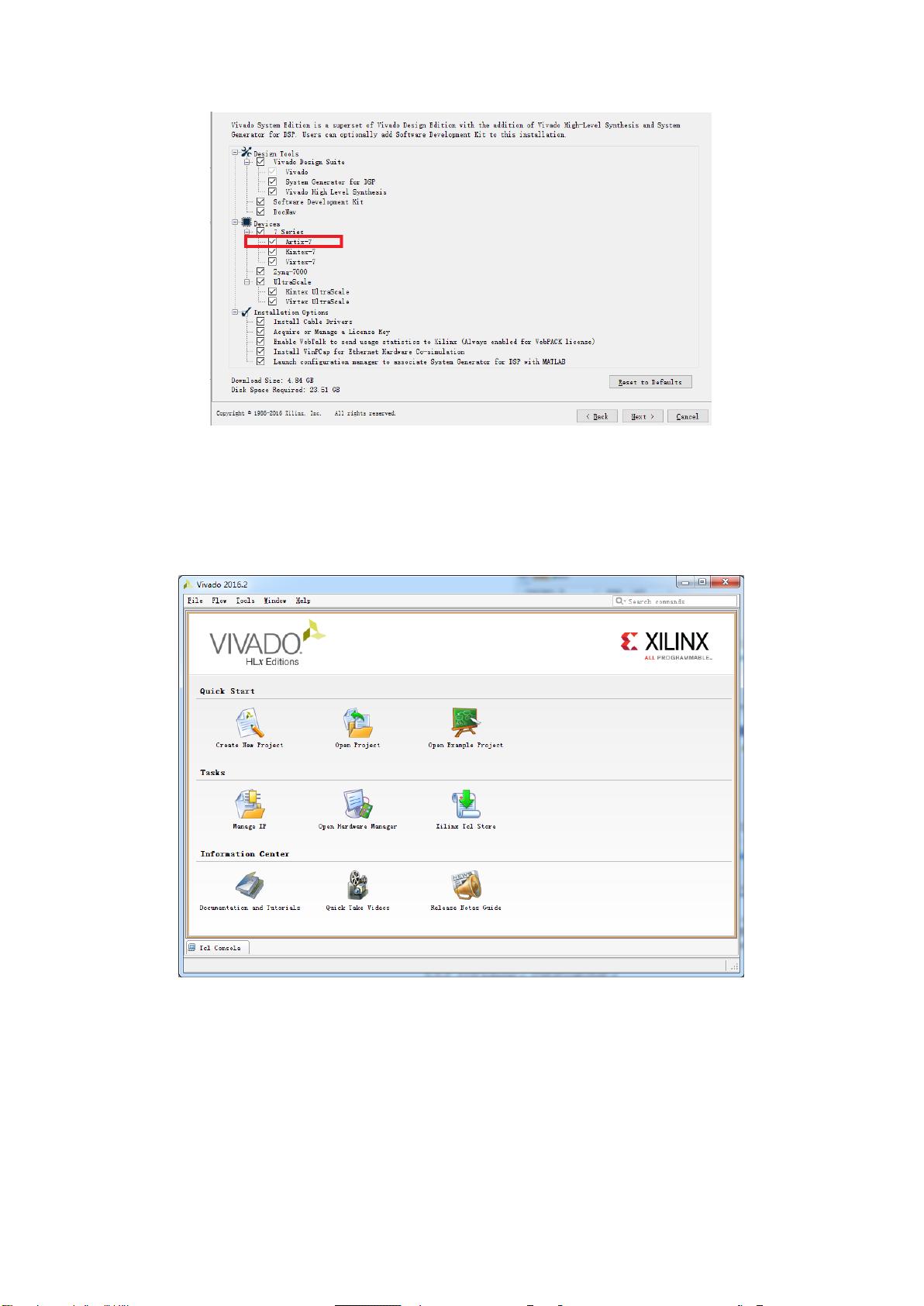

1. 掌握Vivado软件的基本操作,例如下载、安装和使用教程。

2. 学习如何使用Verilog编写仿真文件,理解代码如何映射到实际电路中。

3. 学习通过Verilog仿真观察和分析波形,以判断电路功能的正确性。

实验环境的要求包括一台PC,运行Windows或Linux操作系统,以及访问Vivado工具的权限,例如vlab.ustc.edu.cn网站提供的教程和下载资源。实验步骤具体分为:

1. 下载并安装Vivado,根据个人操作系统选择对应版本,可以选择支持Airtex-7系列芯片的版本以节省存储空间。

2. 在安装过程中,了解并配置软件以适应实验平台的特定芯片型号。

总结来说,实验05不仅涉及到了理论学习,如电路设计原理和Verilog语言的理解,还包括了实际操作技能的训练,如使用Vivado进行电路设计验证,这对于理解和优化数字电路设计流程至关重要。通过这个实验,学生将能够更好地掌握FPGA设计和调试的关键环节。

2022-09-23 上传

2022-09-21 上传

2022-07-13 上传

2022-09-24 上传

2022-09-15 上传

2022-09-14 上传

2022-09-24 上传

2021-09-28 上传

2022-08-03 上传