多路ADC系统:DSP与CPLD协同设计详解

175 浏览量

更新于2024-08-28

收藏 172KB PDF 举报

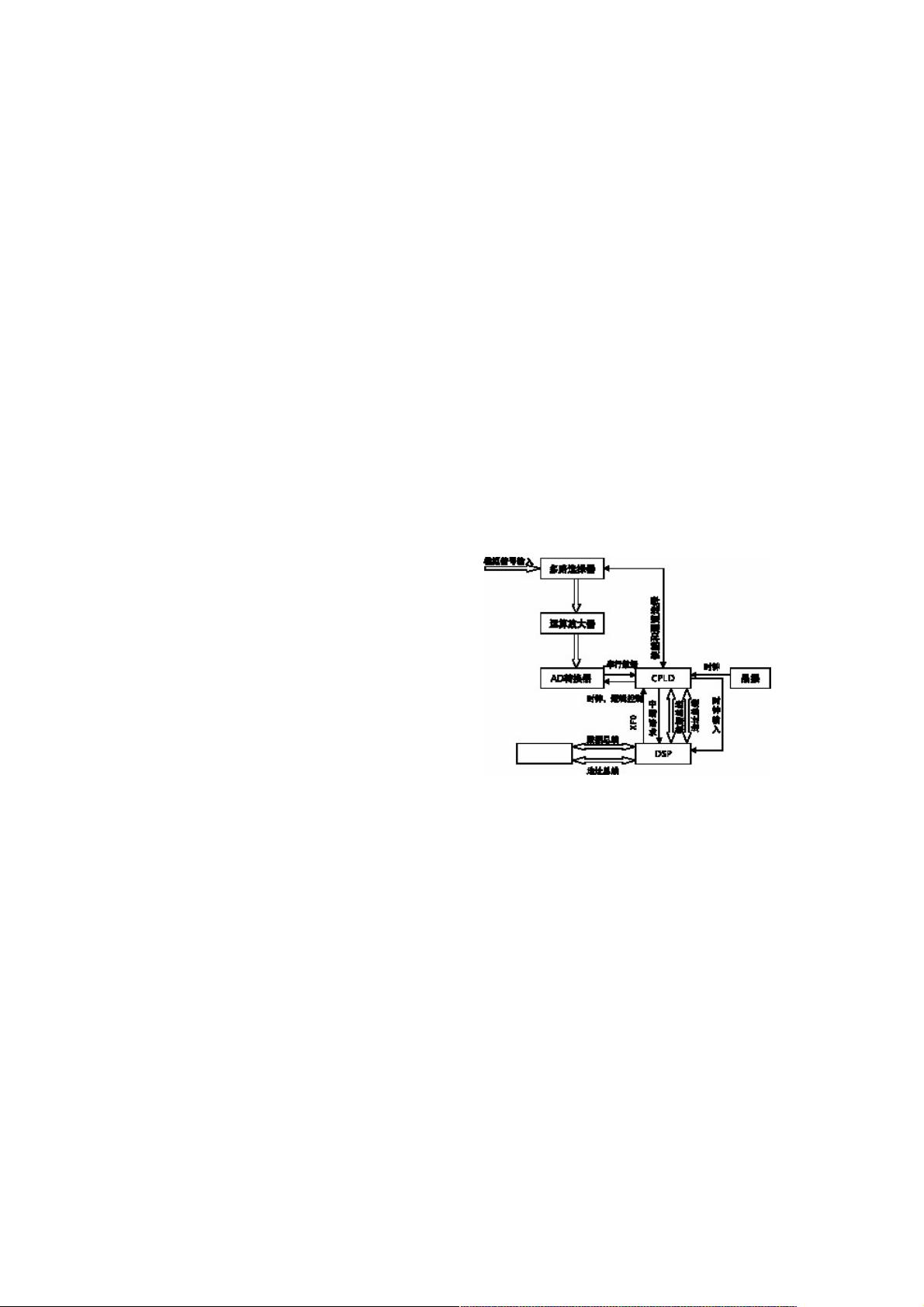

本文主要探讨了基于DSP (Digital Signal Processor, 数字信号处理器) 和CPLD (Complex Programmable Logic Device, 复杂可编程逻辑器件) 技术的多路ADC (Analog-to-Digital Converter, 模拟到数字转换器) 系统的设计与实现。在引言部分,文章指出随着电子技术的发展,多路ADC系统的需求增长,因为它们能够处理复杂多路模拟输入信号,提高数据采集和处理的效率,同时也简化了电路设计。

系统的核心是采用了Maxim公司生产的低功耗16位逐次逼近型ADC器件MAX1162。这款ADC具有自动关断功能,可以节省能源,快速唤醒时间仅为1.1μs,支持SPI/QSPI/Microwire等多种高速接口,确保了数据传输的高效性。MAX1162的工作电压为+5V,配备独立的数字电源引脚,可以兼容宽范围的数字逻辑接口。模拟输入信号通过ref引脚连接外部参考电压,模拟地则与4.7μf的电解电容相连,以稳定信号。

ADC的控制部分采用TI公司的TMS320VC33-150浮点数字信号处理器,它提供了24位地址总线,这意味着系统拥有强大的数据处理能力。通过TMS320VC33-150,系统可以协调MAX1162的采样、转换和数据传输,实现对模拟信号的精确控制和处理。

此外,文章还详细描述了硬件设计中的其他关键组件,如串行时钟(sclk)用于驱动ADC转换过程,数据输出(dout)用于接收转换后的数字数据,数字地(dgnd)和数字电源(dvdd)确保了系统的稳定运行。模拟信号输入端(ain)直接连接到模拟信号源,cs作为片选信号,控制ADC的启用和休眠状态。

本文探讨了如何结合DSP和CPLD技术,构建一个高效、低功耗且具有良好通用性和可移植性的多路ADC系统,其核心是高效的ADC器件和智能的数字信号处理器的协同工作,这对于现代电子系统中复杂信号处理应用具有重要意义。

2020-08-13 上传

2020-08-05 上传

2020-11-26 上传

点击了解资源详情

点击了解资源详情

2023-05-26 上传

2024-01-24 上传

2023-06-05 上传

2023-09-28 上传

weixin_38655347

- 粉丝: 9

- 资源: 919

最新资源

- WebLogic集群配置与管理实战指南

- AIX5.3上安装Weblogic 9.2详细步骤

- 面向对象编程模拟试题详解与解析

- Flex+FMS2.0中文教程:开发流媒体应用的实践指南

- PID调节深入解析:从入门到精通

- 数字水印技术:保护版权的新防线

- 8位数码管显示24小时制数字电子钟程序设计

- Mhdd免费版详细使用教程:硬盘检测与坏道屏蔽

- 操作系统期末复习指南:进程、线程与系统调用详解

- Cognos8性能优化指南:软件参数与报表设计调优

- Cognos8开发入门:从Transformer到ReportStudio

- Cisco 6509交换机配置全面指南

- C#入门:XML基础教程与实例解析

- Matlab振动分析详解:从单自由度到6自由度模型

- Eclipse JDT中的ASTParser详解与核心类介绍

- Java程序员必备资源网站大全