S3C2440嵌入式系统时钟体系详解与代码分析

下载需积分: 9 | 867KB |

更新于2024-09-06

| 164 浏览量 | 举报

收藏

立即下载

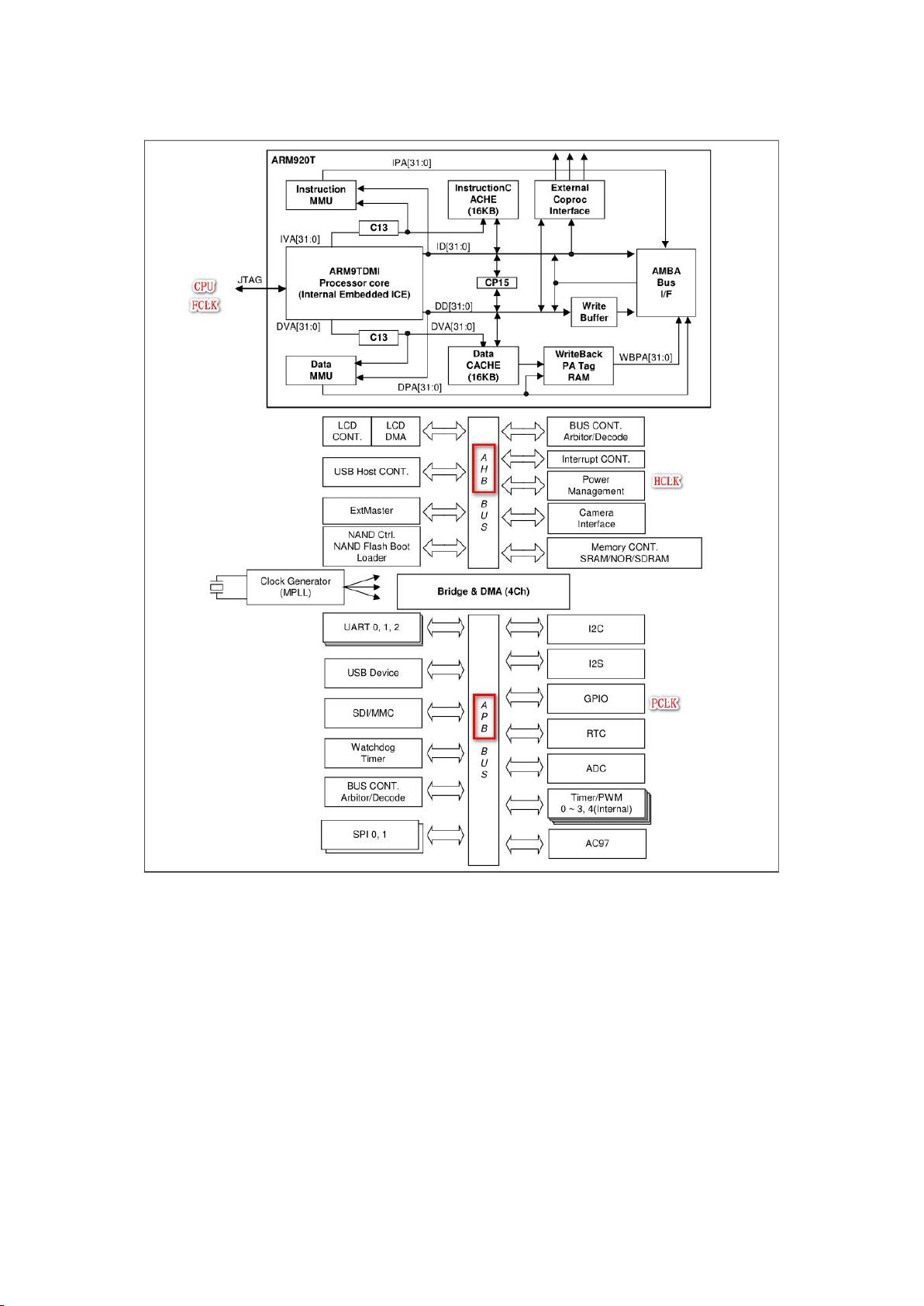

立即下载 本文档深入解析了ARM嵌入式系统中S3C2440芯片的时钟体系结构,对于理解和开发基于ARM的低功耗嵌入式应用至关重要。S3C2440作为一个典型的System-on-Chip (SoC),集成了CPU和其他外设,这些外设分为两类:高速外设挂载在AHB总线,使用HCLK时钟,速度可达136MHz;低速外设则挂载在APB总线,使用PCLK时钟,速度可达68MHz。

核心时钟系统包括三个主要部分:FCLK(用于CPU),HCLK(高速外设),和PCLK(低速外设)。FCLK的最大频率可达400MHz,是系统的核心时钟。时钟的获取源于外部12MHz晶振,通过S3C2440的两个PLL(MPLL和UPLL)进行倍频和分频,以便满足不同外设的需求。MPLL和UPLL的选择器OM[3:2]配置为00,确保两者都使用外部12MHz晶振作为基准,然后通过控制寄存器调整输出频率。

时钟控制逻辑涉及复位过程。当系统上电时,复位引脚会被外部电路维持在低电平状态,直到电源稳定后,IMP811T芯片会解除复位,将引脚设置为高电平。这种设计确保了系统在初始化期间的稳定性,避免了因快速上电导致的问题。

此外,文档中还包含了相关的代码示例,读者可以通过实际操作和分析这些代码,更好地理解时钟体系的工作原理。这对于硬件开发者和嵌入式系统工程师来说,是一份极具价值的学习资料,能够帮助他们优化系统的性能和功耗,提升设计效率。

相关推荐

亮子哲也

- 粉丝: 4

最新资源

- Weblogic功能详解及使用手册

- 软件自动化测试资料分析与应用

- C++实现Joseph问题:nlgn时间算法与平衡二叉树

- VB字符判断程序:菜鸟的实践与交流

- 掌握Lucene全文索引:搜索实例演示

- Helloer_v1.8版发布:全面的技术文档与安装资源

- 掌握NS2网络仿真工具:步骤与分析

- Proteus仿真Max7221动态显示实用教程

- C#纸业销售管理系统开发与下载指南

- LWUIT J2ME界面设计实例与Eclipse项目转换

- MP3剪切软件工具:轻松编辑你的音乐文件

- JSP与SQL结合的人事管理系统开发教程

- 梁昆淼数学物理方法习题解答精编

- 批量将Word文档转换为Flash文档工具

- Pbkiller 2.5.8:Powerbuilder文件反编译神器

- USB开发基础教程与驱动结构分析

- 掌握CVS使用与安装:完整基础教程与软件下载

- 网页制作遇到的问题与解决方案集锦

- L7手机连接必备:高效USB驱动安装指南

- C#实现的人力资源管理系统代码分析

- MFC实现ODBC数据库闹钟功能

- Win32系统服务开发深度解析与实战案例

- Java+Swing开发的企业人事管理系统研究

- 计算机行业翻译利器:专业英语翻译软件