Zynq UltraScale+ RFSoC数据转换器v2.4详细指南

本文档是关于Xilinx Zynq UltraScale+ RFSoC (Radio Frequency System on Chip) RF Data Converter v2.4的详细用户指南(PG269)。这份手册提供了关于这款IP核的核心信息、功能概述、产品规格、设计流程以及应用实例。

1. **IP事实与特点**:

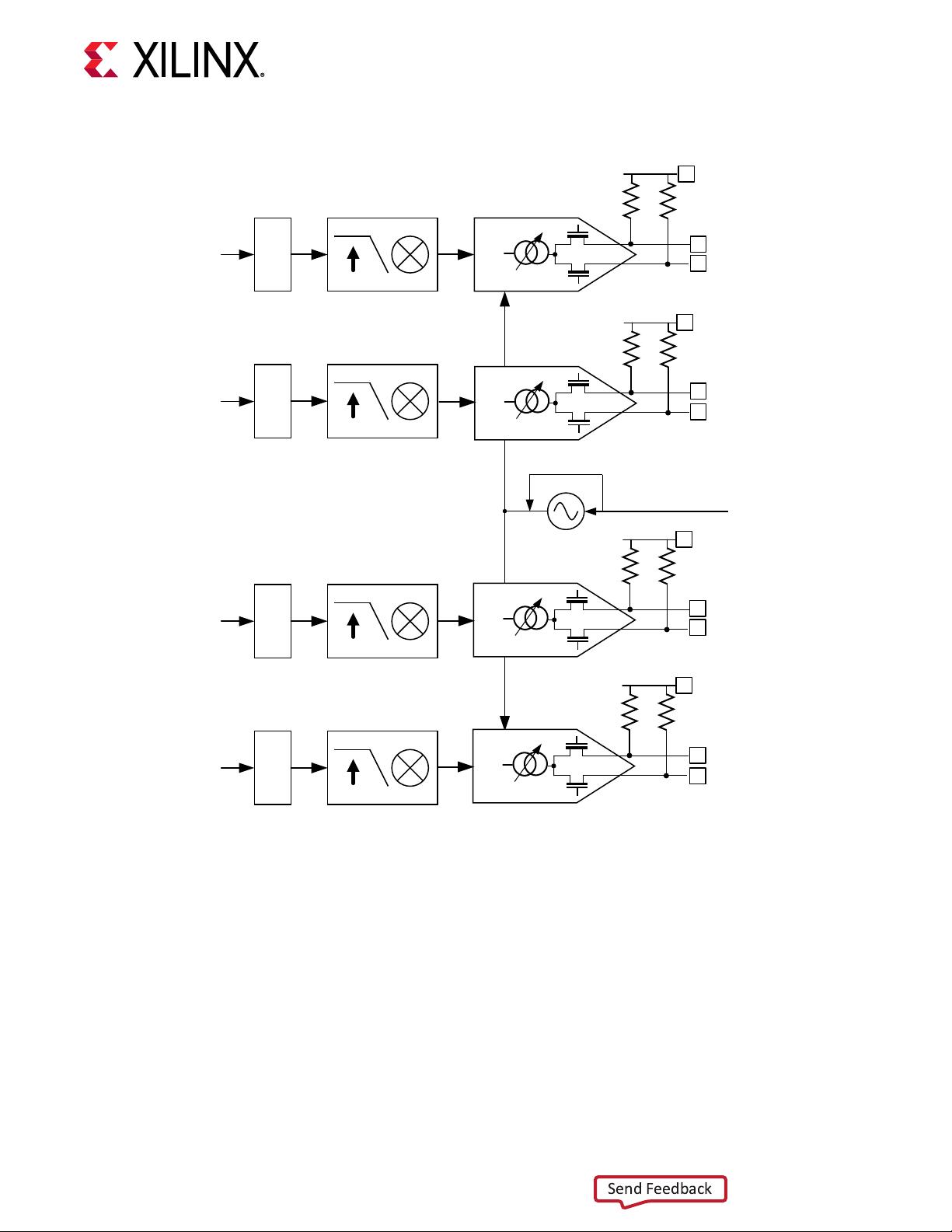

本章介绍了IP核的基本特性,包括其在Zynq UltraScale+ RFSoC平台上的优势。它可能是针对高精度射频信号处理的,具有先进的RF-ADC (Radio Frequency Analog-to-Digital Converter) 和 RF-DAC (Radio Frequency Digital-to-Analog Converter),用于无线通信、雷达系统或信号处理应用中的数据转换。

2. **设计流程导航**:

手册指导用户通过设计流程,从IP Core配置到软件驱动,再到实际应用中的接口配置,如AXI4-Stream接口。章节间内容逻辑清晰,便于设计师逐步实施项目。

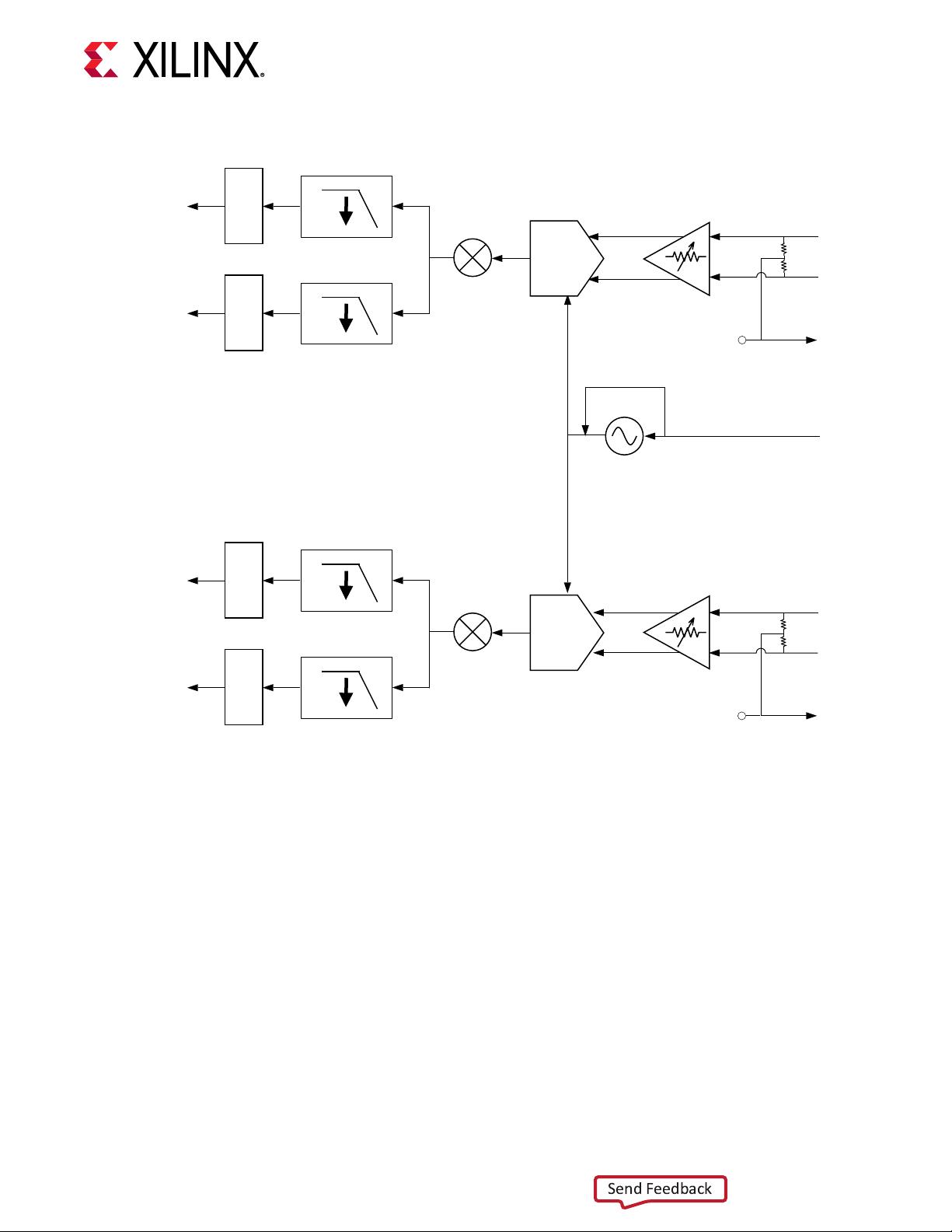

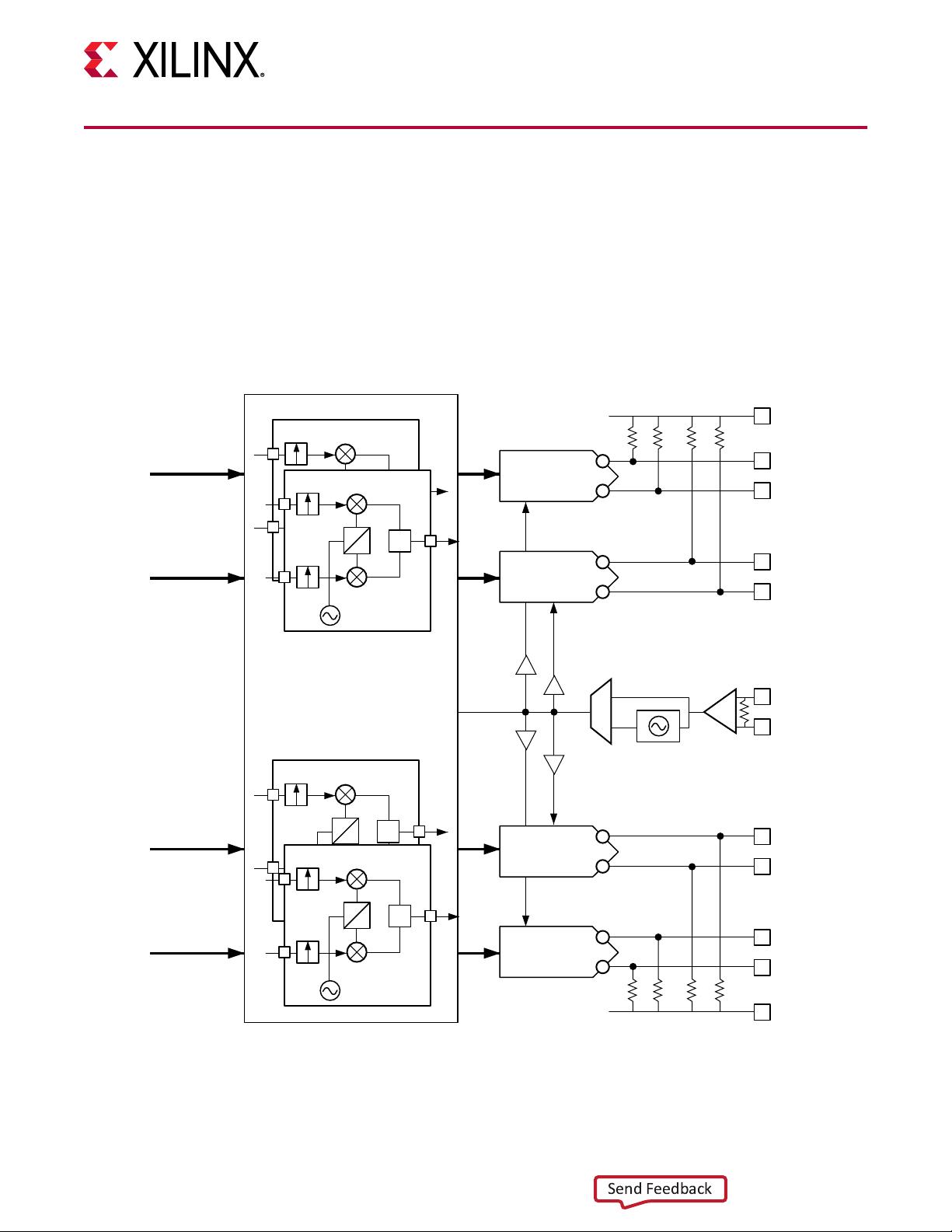

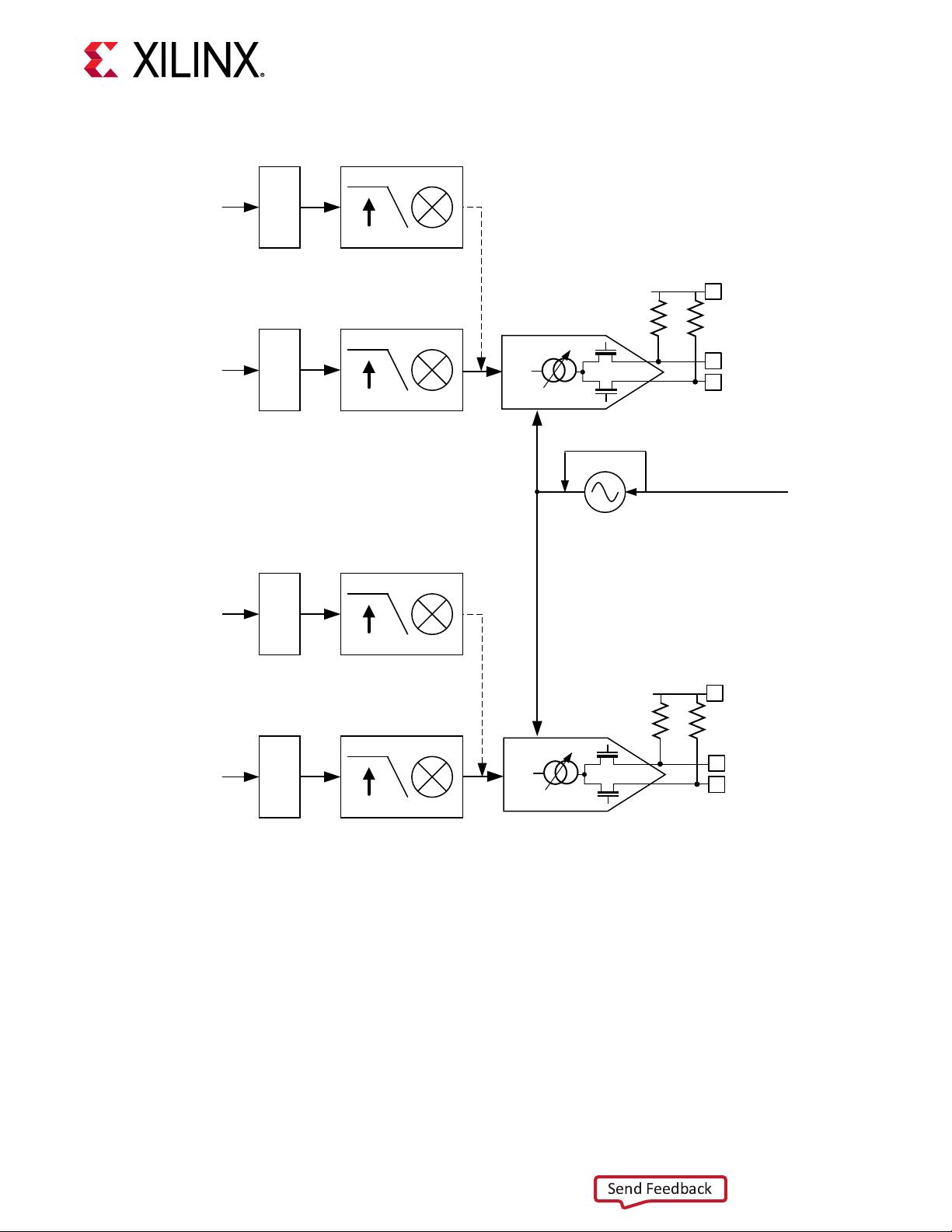

3. **RF-ADC与RF-DAC**:

详细说明了这两个关键模块的功能和技术细节,可能涉及采样率、分辨率、动态范围和功耗等性能指标。同时,还可能涉及如何进行模数和数模转换,以及如何校准以实现精确的数据转换。

4. **设计步骤与定制**:

在第5章,文档概述了设计流程,包括如何在Vivado Design Suite中定制IP核,模拟验证,以及合成和实施步骤。这有助于开发者理解如何把IP核融入整体系统设计。

5. **产品规格**:

第3章涵盖了IP核的具体性能参数,如数据吞吐量、功耗、资源占用情况等,以及端口描述和寄存器空间,这对于评估其在具体硬件平台上的适用性和资源需求至关重要。

6. **PLL与中断处理**:

关键技术部分,如PLL (Phase-Locked Loop)的使用和中断处理机制,确保了系统的时钟稳定性和异常事件的正确响应。

7. **电源管理与模式支持**:

提供了电源上电序列以及对于单工(TDD, Time Division Duplexing)和双工(FDD, Frequency Division Duplexing)模式的特定设置,适应不同的通信协议和应用场景。

8. **位流重配置**:

对于可能需要根据需求动态调整的IP核,手册解释了如何进行位流重新配置,以实现灵活的设计。

这份"rfsoc ip核手册"是一份全面且深入的技术文档,为开发人员提供了关于Xilinx Zynq UltraScale+ RFSoC RF Data Converter v2.4的完整设计指南,无论是在选择、集成还是优化该IP核时,都能提供宝贵的信息和参考资料。

221 浏览量

点击了解资源详情

123 浏览量

496 浏览量

358 浏览量

925 浏览量

353 浏览量

1209 浏览量

443 浏览量

FPGA_Linuxer

- 粉丝: 1510

- 资源: 4

最新资源

- 基于卷积神经网络的4种猫咪预测模型

- 中交进出库明细表excel模版下载

- 使用Arduino监控ECG和呼吸-项目开发

- ya-school-shri-2018-1:“发现错误”-接口开发学院的入门作业

- DailyGrain

- 镍矿开采:一种用于收集镍矿开采场所相关数据的模型。 工作正在进行中

- 女士闺房3D模型设计

- 工程管理人员个人总结

- HTML-CSS-[removed]实行多元化的保护措施

- 128x64 LCD上的模拟,数字时钟和温度计-项目开发

- Smolyak各向异性网格:解决高维问题-matlab开发

- terraform-workshop

- 日记账管理系统excel模版下载

- 酒店走廊3D模型

- Arduino 101-英特尔居里图案匹配连衣裙-项目开发

- Ecom