2014年Atrenta研讨会:解决IC设计中的跨时钟域问题与Atrenta SpyGlass解决方案

需积分: 12 124 浏览量

更新于2024-07-14

收藏 3.55MB PDF 举报

在2014年4月的CDC研讨会上,演讲者Shaker Sarwary讨论了在IC设计中至关重要的"跨时钟域检查"(Cross-Clock Domain Communication, CDC)问题。随着现代集成电路设计的复杂性增加,特别是在无线、网络、视频和图形处理等异构应用中,系统中的时钟数量急剧增长,导致大量的异步接口和时钟域交互。这带来了许多挑战,包括数据传输的安全性、系统行为的稳定性以及潜在的设计陷阱。

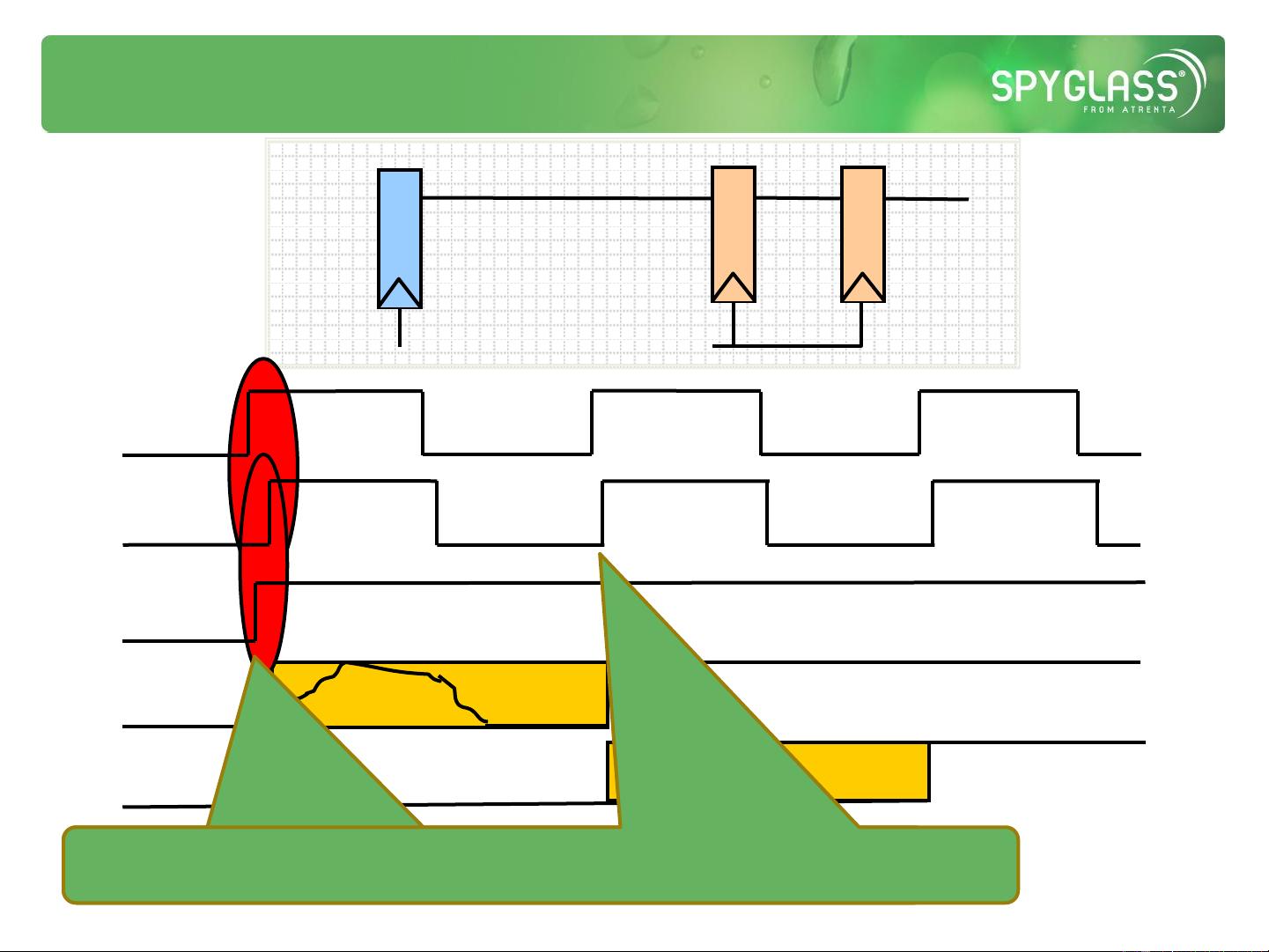

会议首先强调了meta-stability( metastability,也称暂稳态或竞争冒险)对系统性能的影响。在同步设计中,逻辑计算依赖于时钟边沿,确保数据稳定传输并满足setup/hold时间。然而,当数据源D1由另一个异步时钟驱动时,这个问题变得复杂。此时,输入到组合逻辑的变化可能会在Ck2时钟边沿触发瞬态毛刺,即暂态错误,这对信号完整性(Signal Integrity, SI)和功能正确性都构成威胁。

传统的电子设计自动化工具(如静态时序分析STA和功能验证)往往无法充分检测这些异步接口的问题。因此,有效的CDC验证变得至关重要。Atrenta公司提出了其SpyGlass CDC解决方案,这是一个专门针对时钟域交互进行深入分析的工具。该方案旨在帮助设计师识别并消除潜在的杀手级错误,比如数据丢失、数据翻转或者延迟,以确保芯片的可靠性和性能。

会议上还探讨了良好的设计实践,包括在设计阶段就考虑到异步接口的影响,合理规划时钟网络,以及使用适当的时钟门控技术来减少暂稳态问题。同时,演讲者也提到了当前面临的挑战,如如何处理大量时钟的复杂性,以及如何跟上快速发展的验证技术和趋势。

这次研讨会提供了一个全面的视角,展示了在现代IC设计中跨时钟域检查的重要性,以及如何通过工具和技术来有效地应对这一挑战,以避免设计缺陷和提升整体设计质量。通过理解这些知识点,工程师可以更好地预防和解决异步接口中的问题,确保产品的高性能和可靠性。

2022-08-08 上传

2023-07-21 上传

2023-07-21 上传

汪芯人

- 粉丝: 0

最新资源

- 小学水墨风学校网站模板设计

- 深入理解线程池的实现原理与应用

- MSP430编程代码集锦:实用例程源码分享

- 绿色大图幻灯商务响应式企业网站开发源码包

- 深入理解CSS与Web标准的专业解决方案

- Qt/C++集成Google拼音输入法演示Demo

- Apache Hive 0.13.1 版本安装包详解

- 百度地图范围标注技术及应用

- 打造个性化的Windows 8锁屏体验

- Atlantis移动应用开发深度解析

- ASP.NET实验教程:源代码详细解析与实践

- 2012年工业观察杂志完整版

- 全国综合缴费营业厅系统11.5:一站式缴费与运营管理解决方案

- JAVA原生实现HTTP请求的简易指南

- 便携PDF浏览器:随时随地快速查看文档

- VTF格式图片编辑工具:深入起源引擎贴图修改