同步电路设计与可靠性:Verilog教程详解

下载需积分: 4 | PDF格式 | 1.55MB |

更新于2024-08-01

| 192 浏览量 | 举报

本资源是一份关于Verilog教程的详细指南,由华为提供,旨在教授大规模逻辑设计中同步电路设计技术和相关规则。教程的核心内容包括:

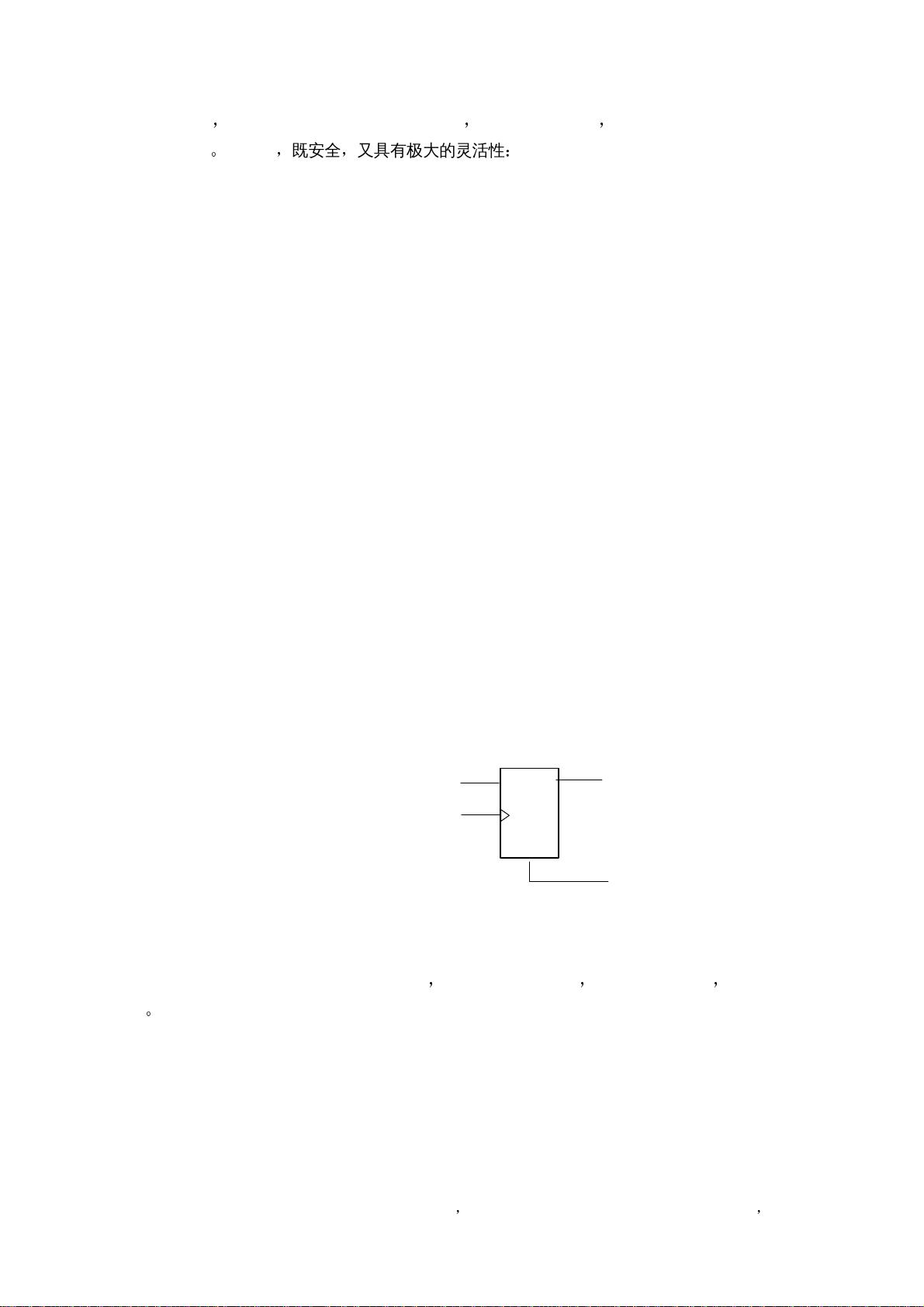

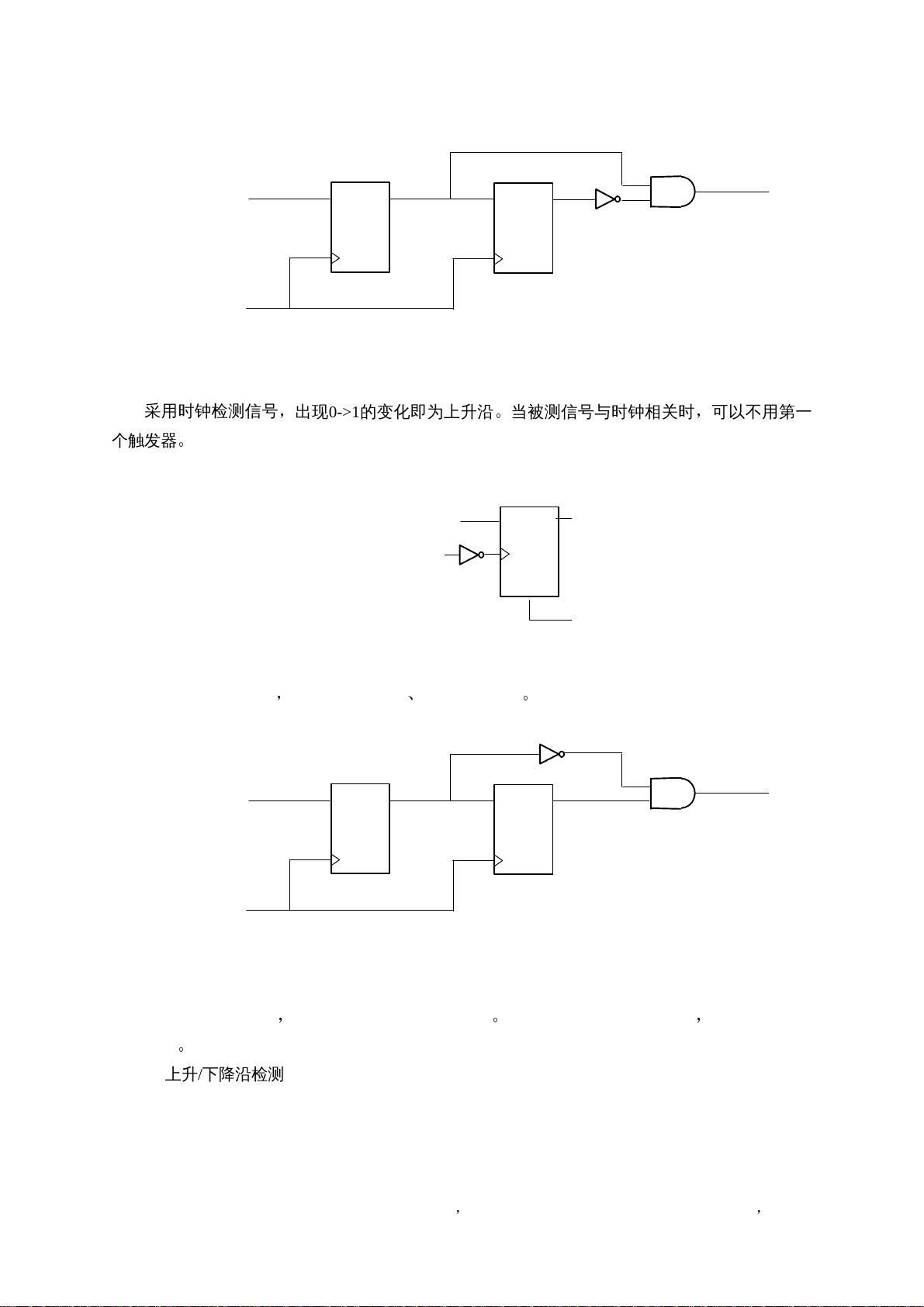

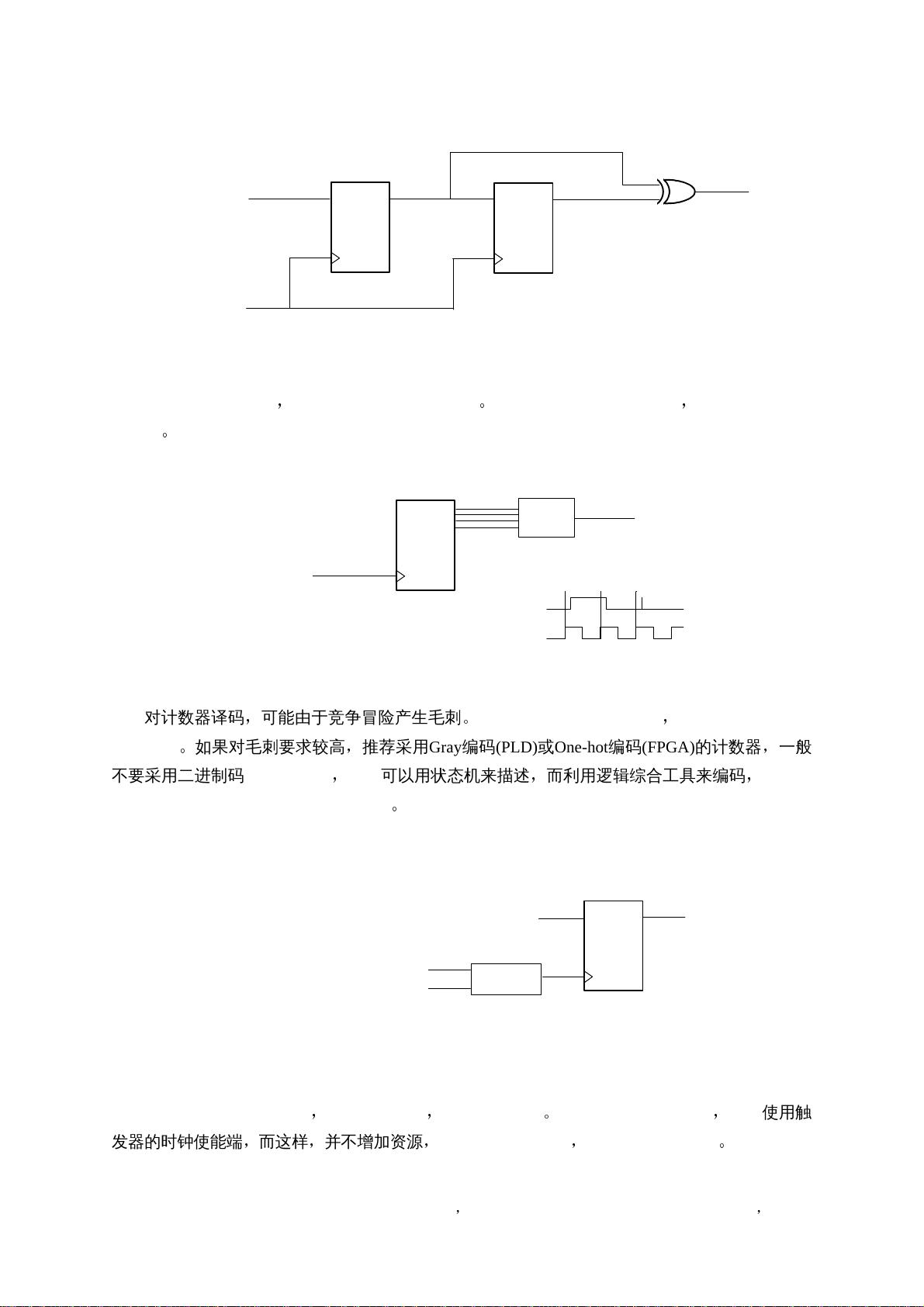

1. 设计可靠性:在可编程逻辑器件设计中,为了增强电路稳定性,同步电路设计被优先推荐。异步电路的设计需明确无法转化为同步的原因,并对时钟信号质量、建立-保持时间和毛刺等问题进行详尽分析。时钟周期、延迟和触发器的建立/保持时间是关键参数,它们决定了电路的时序性能。

2. 时序分析基础:电路设计中,时序分析是难点所在,涉及确保触发器的建立时间和保持时间得到满足。通过图示解释,如REG2为例,T_setup和T_hold的时间关系直接影响信号是否能在时钟周期内正确工作。在同步设计中,全局时钟的存在大大减少了T带来的影响,而在异步设计中,局部时钟可能导致不稳定性和不确定性。

3. 同步电路设计:

- 同步电路的优势在于易于利用寄存器的异步复位/置位端,确保电路初始化的一致性。

- 同步设计有助于避免因时钟问题引发的时序冲突,提升电路的可靠性和性能。

4. 示例与分析:教程提供了具体的电路结构示例(如图1.1和图1.2),通过这些图形,读者可以直观地理解时序分析的过程和不同设计模式下时序约束的处理。

这份华为的大规模逻辑设计指导书深入浅出地讲解了Verilog中同步电路设计的关键要素和技术,对于从事该领域设计的工程师来说,是提高设计质量和效率的重要参考资料。无论是理论阐述还是实例演示,都旨在帮助读者掌握如何在实际项目中有效地应用同步电路设计原则。

相关推荐

13 浏览量

8 浏览量

longonly120

- 粉丝: 4

- 资源: 17

最新资源

- E.rar_clamped inverter_e inverter_three level inverter_三电平电路_二极管

- images:图片

- apkUpdate:基于jfinal框架实现的一个APK更新系统

- .doom.d

- html5小鸟快飞游戏源码下载

- OlegMolchnovTutorial:追随

- 运行智能

- 非常实用的html5实现问答系统源码下载

- FennecBot

- 算法,算法工程师,matlab

- HibernateJPA_HerenciaSingleTable:简单表映射

- 通道打包:将纹理打包到图像RGBA通道中的软件

- eclipse中的hibernate插件

- find-home-ui

- AlphaTcl-开源

- 行业文档-设计装置-一种带通气孔的包装纸箱.zip