PCIe 3.0电气层规范详解与兼容要求

需积分: 9 187 浏览量

更新于2024-07-09

收藏 334KB PDF 举报

本文档详细介绍了PCIe 3.0物理层(PHY)的要求,由Dan Froelich代表Intel Corporation编写,版权归属于PCI-SIG。PCIe 3.0是PCI Express标准的最新版本,旨在提供更快的数据传输速度和更严格的电气规范。以下是文档中的关键知识点:

1. **PHY Requirements**:物理层规范着重于确保信号的正确传输,包括线路特性、信号完整性、电源管理以及噪声容限。它规定了数据传输的比特率和信号质量的标准。

2. **Preliminary Jitter Budget**:为了实现高速数据传输,对时钟抖动有严格的限制,预设的抖动预算有助于确保信号的同步性。

3. **Statistical Simulation Tools**:文档强调了使用统计模拟工具在设计过程中的重要性,这些工具用于评估系统的可靠性,确保信号在各种环境条件下都能正常工作。

4. **3.0 PHY Rate**:PCIe 3.0的带宽显著提升,数据传输速率达到了16 GT/s,比前一代提高了近3倍,这对硬件设计提出了更高的性能要求。

5. **Transmitter Specification**:包括9 PLL Bandwidth(锁相环带宽)、Reference Location(参考位置)和Timing Parameters(时序参数),这些参数定义了发送器的性能指标,如频率稳定性、上升时间和过冲时间等。

6. **Equalization**:为了补偿线路中可能产生的信号衰减和失真,文档要求支持有效的均衡技术,以保持信号质量。

7. **Reference Clock Specification**:对于精确的时钟同步,规定了参考时钟的精度和稳定性,这对于整个系统的时间基准至关重要。

8. **Receiver Specification**:接收器部分关注噪声抑制、信号检测和错误检测能力,以确保数据的可靠接收。

9. **Backwards Compatibility**:PCIe 3.0必须与Gen1和Gen2兼容,允许在Gen3插槽中以Gen1/Gen2的速度运行,同时支持多种时钟架构。

10. **Power Consumption**:尽管性能增强,但低功耗仍是重要考虑因素,必须在满足性能的同时控制PHY的能耗。

11. **Cost and Manufacturing Considerations**:新标准无需大规模改动现有的连接器、时钟源、材料和高体积制造流程,有利于成本控制和简化生产。

12. **Extreme Server Channels**:尽管如此,极端服务器应用场景可能需要针对特定通道进行优化,以适应更高的带宽需求。

13. **Bit Error Rate (BER) and Data Rates**:目标是达到E-12或更低的误码率,至少提供两倍于PCIe 2.0的有效数据速率,即10 GT/s。

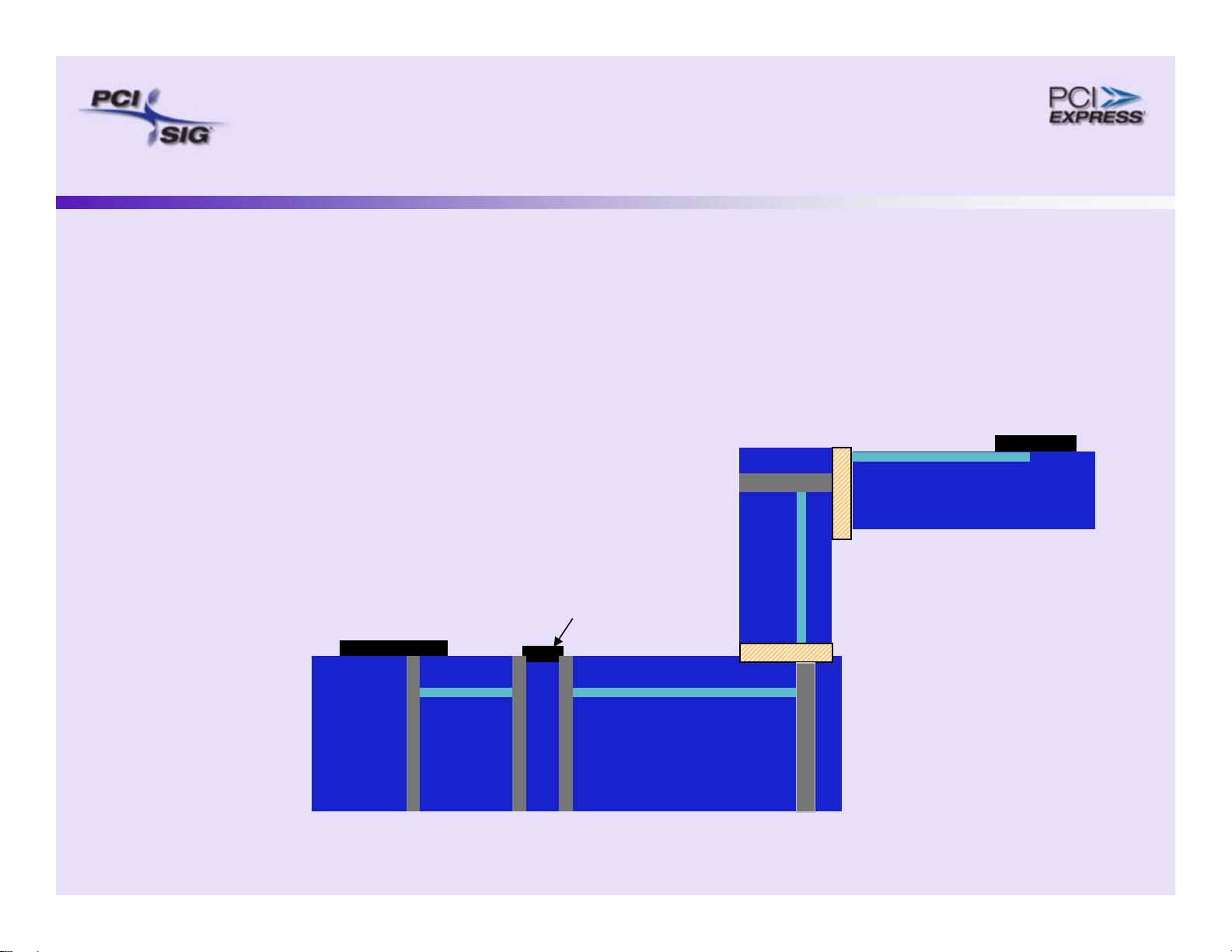

14. **Channel Layout and Signal Integrity**:文档还关注了通道布局对信号完整性的影响,确保信号能够在长距离和复杂电路板布局下维持良好的性能。

这份文档详细描述了PCIe 3.0物理层的电气要求,旨在保证高速、可靠且兼容的通信,为硬件开发者提供了明确的设计指导。

922 浏览量

181 浏览量

128 浏览量

226 浏览量

114 浏览量

2022-09-20 上传

1222 浏览量

443 浏览量

151 浏览量

Marson-J

- 粉丝: 0

最新资源

- A7Demo.appstudio:探索JavaScript应用开发

- 百度地图范围内的标注点技术实现

- Foobar2000绿色汉化版:全面提升音频播放体验

- Rhythm Core .NET库:字符串与集合扩展方法详解

- 深入了解Tomcat源码及其依赖包结构

- 物流节约里程法的文档整理与实践分享

- NUnit3.vsix:快速安装NUnit三件套到VS2017及以上版本

- JQuery核心函数使用速查手册详解

- 多种风格的Select下拉框美化插件及其js代码下载

- Mac用户必备:SmartSVN版本控制工具介绍

- ELTE IK Web编程与Web开发课程内容详解

- QuartusII环境下的Verilog锁相环实现

- 横版过关游戏完整VC源码及资源包

- MVC后台管理框架2021版:源码与代码生成器详解

- 宗成庆主讲的自然语言理解课程PPT解析

- Memcached与Tomcat会话共享与Kryo序列化配置指南