RSA算法的VLSI实现:系统级设计与性能优化

版权申诉

16 浏览量

更新于2024-07-05

收藏 2.72MB PDF 举报

本文主要探讨了位级RSA算法的VLSI(Very Large Scale Integration)实现,特别是在现场可编程门阵列(FPGA)和应用特定集成电路(ASIC)设计中的应用。RSA算法,因其基于大数因子分解的特性,是现代数据加密和数字签名安全性的基石。尽管传统的Montgomery模乘算法的改进是研究热点,但随着系统级芯片(SoC)设计的发展,将RSA算法集成到SoC中具有显著的优势。

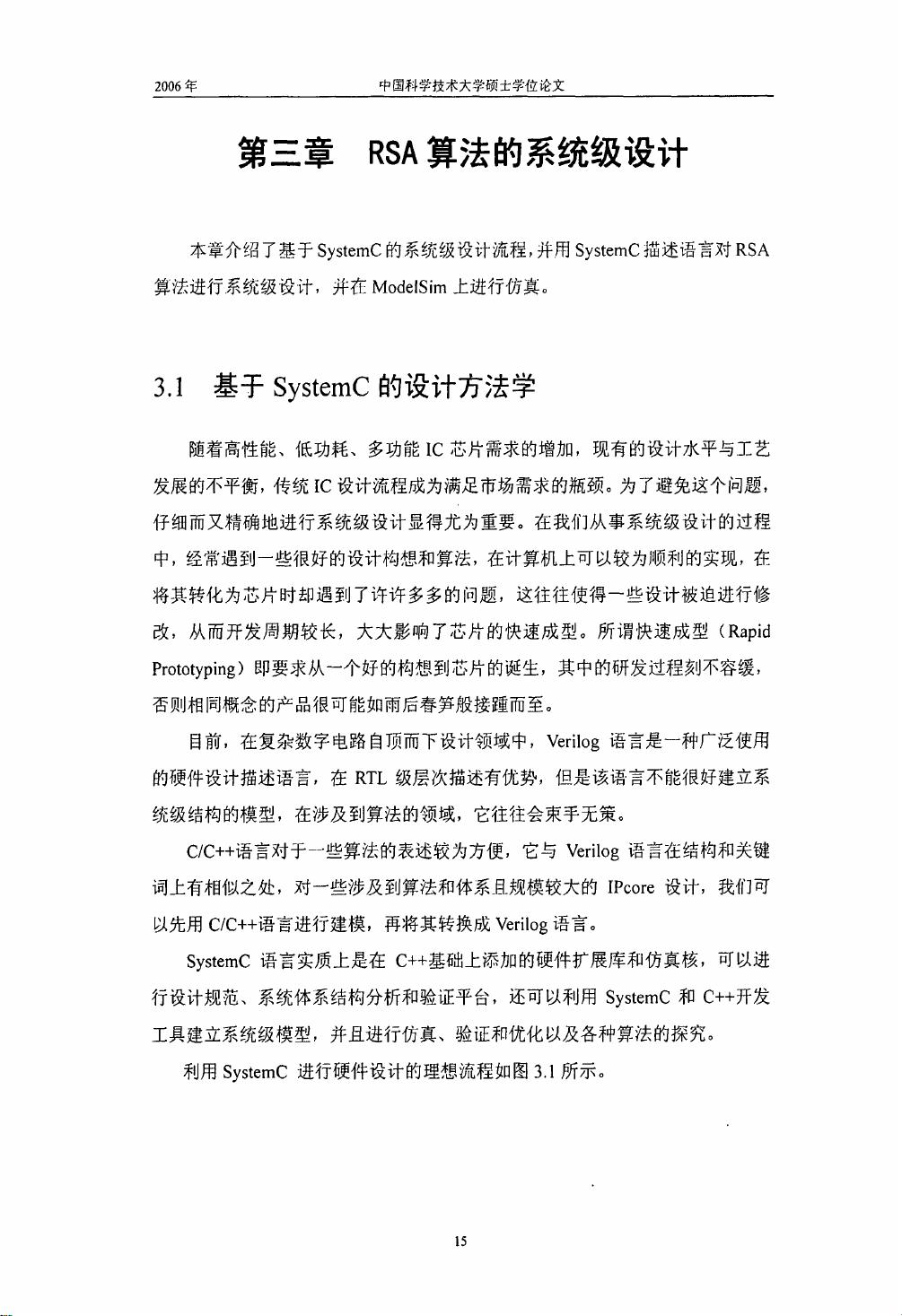

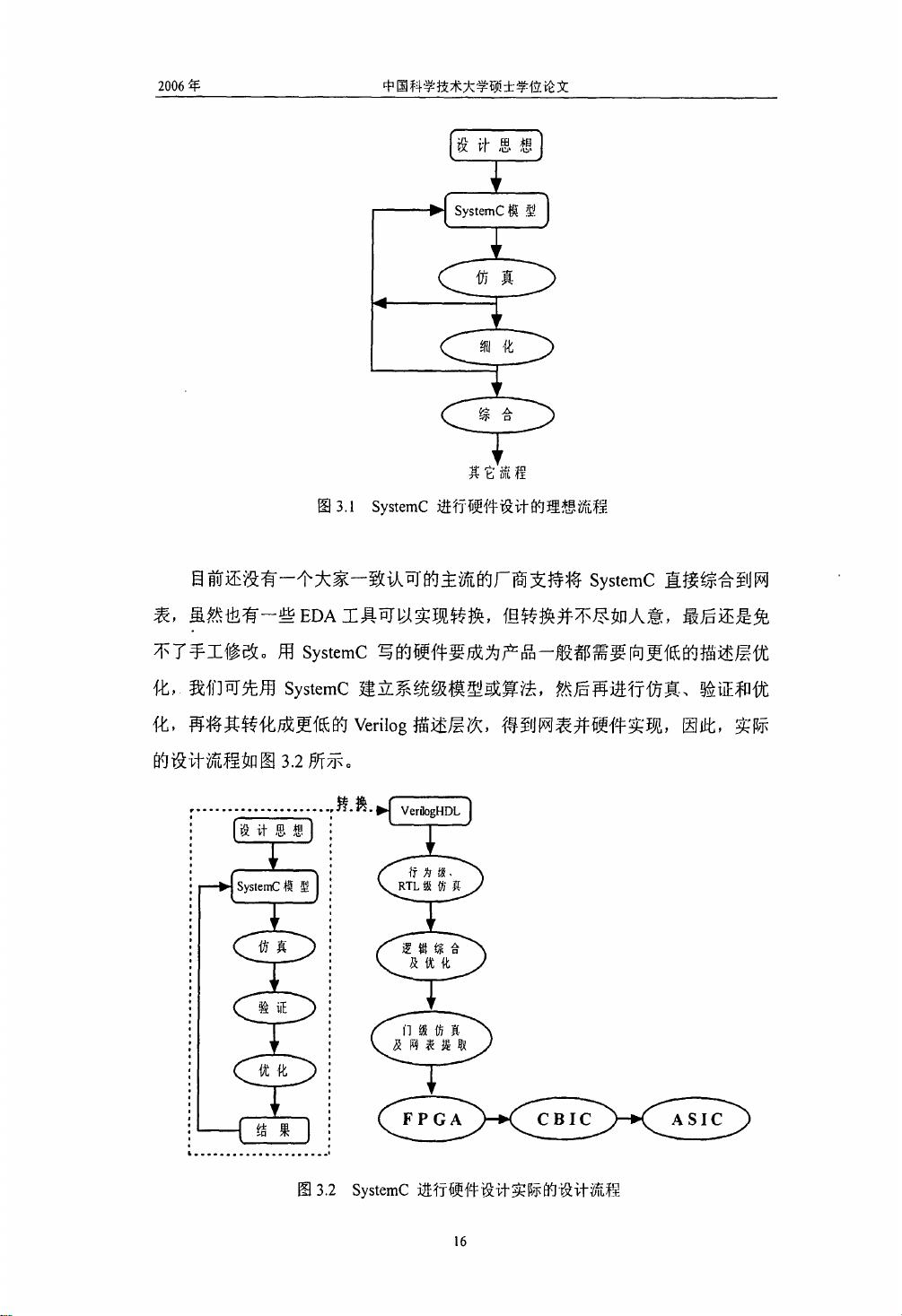

文章首先强调了设计周期和芯片性能对于现代芯片设计的重要性,这两个因素在RSA算法的实现中显得尤为关键。为了缩短设计周期,作者提出了一种基于系统级算法的快速原型设计流程,通过在早期系统设计阶段确定有效的算法并进行评估和优化,可以极大地节省后续RTL(Register Transfer Level)级设计的时间,并为实际芯片制造提供可行性指导。

在提高芯片性能方面,文章创新性地介绍了结合流水线、查找表技术和带有Carry-Save Accumulator (CSA)和Carry-Lookahead Adder (CLA)结构的Montgomery模乘改进算法。这种改进不仅提升了RSA核心运算的速度,而且整体性能得到了显著增强。通过Synopsys的综合工具和SMIC 0.18um工艺库,设计被成功实施。在自行设计的FPGA测试系统中,使用100MHz时钟频率,1024位RSA算法的运算速度达到了每秒约120次,这一速度在不依赖片内微处理器的情况下表现优秀。

当RSA算法融入SoC的快速原型设计流程时,它的高效性能与不断进步的微处理器核心结合,为构建新型基于SoC的设计提供了实用价值。因此,本文不仅提供了RSA算法在硬件实现上的具体步骤和技术细节,也对未来SoC设计中RSA算法的优化和集成策略提出了新的思考方向。关键词包括RSA算法、Montgomery改进算法、设计流程、FPGA以及VLSI技术,这些都表明了研究者对算法效率和集成技术的深入理解和实践探索。

107 浏览量

2021-09-19 上传

155 浏览量

2021-10-09 上传

1006 浏览量

老帽爬新坡

- 粉丝: 99

最新资源

- VB通过Modbus协议控制三菱PLC通讯实操指南

- simfinapi:R语言中简化SimFin数据获取与分析的包

- LabVIEW温度控制上位机程序开发指南

- 西门子工业网络通信实例解析与CP243-1应用

- 清华紫光全能王V9.1软件深度体验与功能解析

- VB实现Access数据库数据同步操作指南

- VB实现MSChart绘制实时监控曲线

- VC6.0通过实例深入访问Excel文件技巧

- 自动机可视化工具:编程语言与正则表达式的图形化解释

- 赛义德·莫比尼:揭秘其开创性技术成果

- 微信小程序开发教程:如何实现模仿ofo共享单车应用

- TrueTable在Windows10 64位及CAD2007中的完美适配

- 图解Win7搭建IIS7+PHP+MySQL+phpMyAdmin教程

- C#与LabVIEW联合采集NI设备的电压电流信号并创建Excel文件

- LP1800-3最小系统官方资料压缩包

- Linksys WUSB54GG无线网卡驱动程序下载指南