没有合适的资源?快使用搜索试试~ 我知道了~

首页高通QCA9563 802.11ac数据手册

80-Y6999-3_QCA9563 802.11N 3X3 2.4 GHZ PREMIUM SOC FOR WLAN PLATFORMS DATA SHEET_.pdf80-Y6999-3_QCA9563 802.11N 3X3 2.4 GHZ PREMIUM SOC FOR WLAN PLATFORMS DATA SHEET_.pdf80-Y6999-3_QCA9563 802.11N 3X3 2.4 GHZ PREMIUM SOC FOR WLAN PLATFORMS DATA SHEET_.pdf80-Y6999-3_QCA9563 802.11N 3X3 2.4 GHZ PREMIUM SOC FOR WLAN PLATFORMS DATA SHEET_.pdf

资源详情

资源评论

资源推荐

Confidential and Proprietary – Qualcomm Atheros Inc.

NO PUBLIC DISCLOSURE PERMITTED: Please report postings of this document on public servers or websites

to: DocCtrlAgent@qualcomm.com.

Restricted Distribution: Not to be distributed to anyone who is not an employee of either Qualcomm or its

subsidiaries without the express approval of Qualcomm’s Configuration Management.

Not to be used, copied, reproduced, or modified in whole or in part, nor its contents revealed in any manner to others

without the express written permission of Qualcomm Atheros, Inc.

Qualcomm is a registered trademark of QUALCOMM Incorporated. Atheros is a registered trademark of Qualcomm

Atheros, Inc. XSPAN is a trademark of Qualcomm Atheros, Inc. All other registered and unregistered trademarks are

the property of QUALCOMM Incorporated, Qualcomm Atheros, Inc., or their respective owners and used with

permission. Registered marks owned by QUALCOMM Incorporated and Qualcomm Atheros, Inc. are registered in

the United States and may be registered in other countries.

This technical data may be subject to U.S. and international export, re-export, or transfer (“export”) laws. Diversion

contrary to U.S. and international law is strictly prohibited.

Qualcomm Atheros, Inc.

1700 Technology Drive

San Jose, CA 95110

U.S.A.

QCA9563 802.11n 3x3 2.4 GHz

Premium SOC for WLAN Platforms

Data Sheet

80-Y6999-3 Rev. E

July 2014

© 2013-2014 Qualcomm Atheros, Inc.

80-Y6999-3 Rev. E MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION 2

Confidential and Proprietary – Qualcomm Atheros Inc.

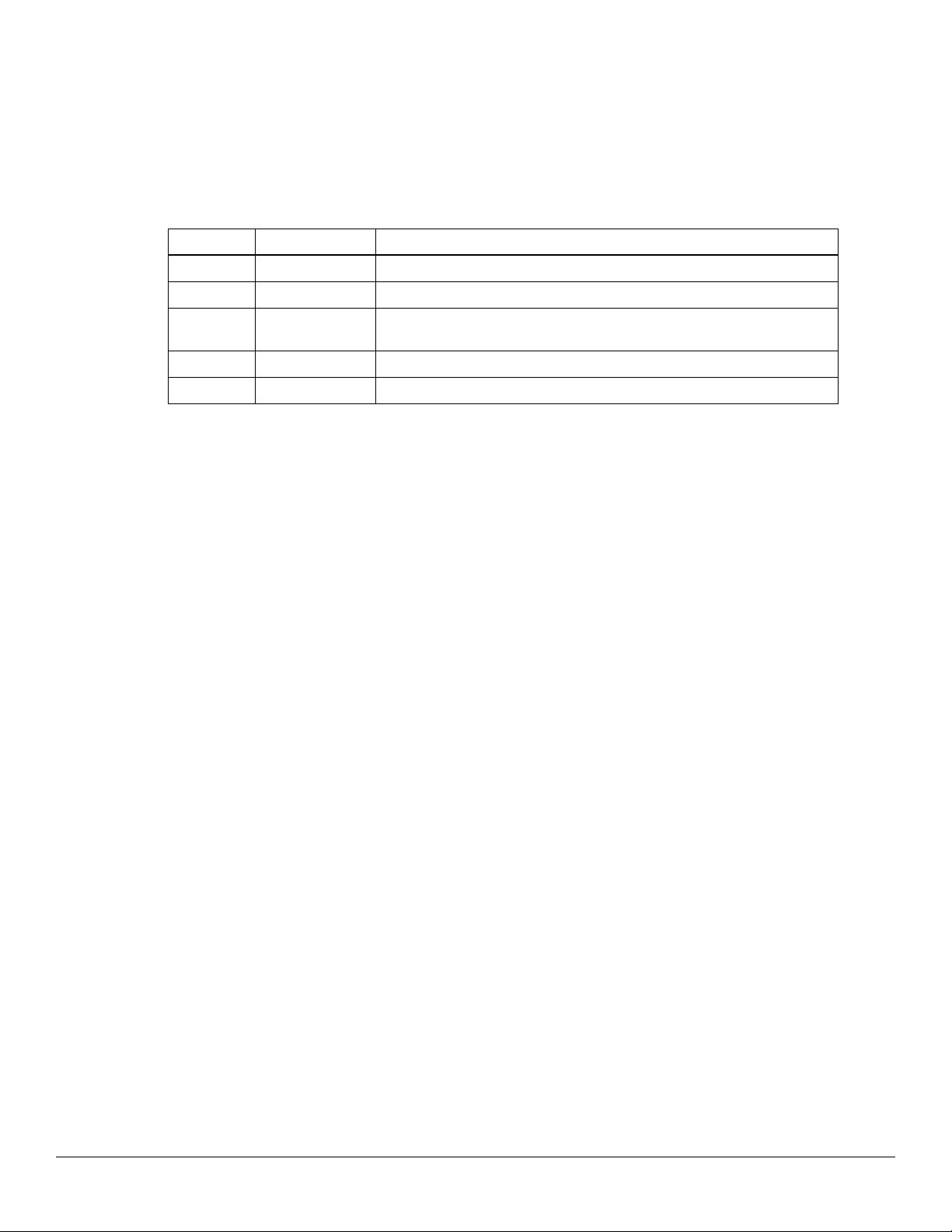

Revision History

Revision Date Description

A October 2013 Initial Release

B January 2014 Added Registers, AC Specifications and electrical information

C March 2014 Added Reliability chapter, tape and reel information, and chip makings

information

D April 2014 Added Reset Register 2 (RST_RESET2), GPIO MUX table

E July 2014 Updated Power Consumption Information

80-Y6999-3 Rev. E MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION 3

Confidential and Proprietary – Qualcomm Atheros Inc.

Contents

1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.2 QCA9563 System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.1 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.2 Bootstrap Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.3 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.4 PLL and Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.4.1 Full Chip Clocking Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.4.2 CPU PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.4.3 DDR PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.4.4 Ethernet PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.5 MIPS Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.6 Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.7 DDR Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.7.1 DDR Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.7.2 DDR Initialization Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.7.3 DDR Memory Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.7.4 CPU DDR Address Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.7.5 Refresh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.7.6 Self Refresh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.8 GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.8.1 GPIO Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.8.2 GPIO Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3.9 Serial Flash SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3.9.1 SPI Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.9.2 Write Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.9.3 Page Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.9.4 Page Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.10 Low-Speed UART Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.11 PCIE RC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.11.1 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

80-Y6999-3 Rev. E MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION 4

Confidential and Proprietary – Qualcomm Atheros Inc.

QCA9563 802.11n 3x3 2.4 GHz Premium SOC for WLAN Platforms Data Sheet Contents

3.11.2 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.11.3 Error Reporting Capability and Status Checking . . . . . . . . . . . . . . . . . . . . . . . 52

3.11.4 Byte-Swap Option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.11.5 Request Sizes and Payloads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.12 USB 2.0 Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4 Radio Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.1 Receiver (Rx) Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

4.2 Transmitter (Tx) Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

4.3 Synthesizer (SYNTH) Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

4.4 Bias/Control (BIAS) Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5 WLAN Medium Access Control (MAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.2 Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.3 Descriptor Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.4 Queue Control Unit (QCU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.5 DCF Control Unit (DCU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.6 Protocol Control Unit (PCU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.7 Register Programming Details for Observing WMAC Interrupts . . . . . . . . . . . . . . . . . . . 79

6 Digital PHY Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

6.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

6.2 802.11n (MIMO) Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

6.2.1 Transmitter (Tx) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.2.2 Receiver (Rx) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

6.3 802.11 b/g Legacy Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

6.3.1 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

6.3.2 Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

7 Ethernet Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

7.1 GMAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

7.1.1 SGMII Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

7.2 GMAC Descriptor Structure: Rx . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

7.2.1 Start Address for Packet Data (PKT_START_ADDR) . . . . . . . . . . . . . . . . . . . 85

7.2.2 Packet Size and Flags (PKT_SIZE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

7.2.3 Next Packet Descriptor Address (NEXT_DESCRIPTOR) . . . . . . . . . . . . . . . . 86

7.3 GMAC Descriptor Structure: Tx . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

7.3.1 Start Address for Packet Data (PKT_START_ADDR) . . . . . . . . . . . . . . . . . . . 87

7.3.2 Packet Size and Flags (PKT_SIZE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

7.3.3 Next Packet Descriptor Address (NEXT_DESCRIPTOR) . . . . . . . . . . . . . . . . 88

8 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

8.1 DDR Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

80-Y6999-3 Rev. E MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION 5

Confidential and Proprietary – Qualcomm Atheros Inc.

QCA9563 802.11n 3x3 2.4 GHz Premium SOC for WLAN Platforms Data Sheet Contents

8.1.1 DDR DRAM Configuration (DDR_CONFIG) . . . . . . . . . . . . . . . . . . . . . . . . . 91

8.1.2 DDR DRAM Configuration 2 (DDR_CONFIG2) . . . . . . . . . . . . . . . . . . . . . . 92

8.1.3 DDR Mode Value (DDR_MODE_REGISTER) . . . . . . . . . . . . . . . . . . . . . . . . 93

8.1.4 DDR Extended Mode (DDR_EXTENDED_MODE_REGISTER) . . . . . . . . . 93

8.1.5 DDR Control (DDR_CONTROL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

8.1.6 DDR Refresh Control and Configuration (DDR_REFRESH) . . . . . . . . . . . . . 94

8.1.7 DDR Read Data Capture Bit Mask (DDR_RD_DATA_THIS_CYCLE) . . . . . 94

8.1.8 DQS Delay Tap Control for Byte 0 (TAP_CONTROL_0) . . . . . . . . . . . . . . . . 94

8.1.9 DQS Delay Tap Control for Byte 1 (TAP_CONTROL_1) . . . . . . . . . . . . . . . . 95

8.1.10 GE0 Interface Write Buffer Flush (DDR_WB_FLUSH_GE0) . . . . . . . . . . . . 95

8.1.11 USB Interface Write Buffer Flush (DDR_WB_FLUSH_USB) . . . . . . . . . . . . 95

8.1.12 PCIE Interface Write Buffer Flush (DDR_WB_FLUSH_PCIE) . . . . . . . . . . . 96

8.1.13 WMAC Interface Write Buffer Flush (DDR_WB_FLUSH_WMAC) . . . . . . . 96

8.1.14 DDR2 Configuration (DDR_DDR2_CONFIG) . . . . . . . . . . . . . . . . . . . . . . . . 96

8.1.15 DDR EMR2 (DDR_EMR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

8.1.16 DDR EMR3 (DDR_EMR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

8.1.17 DDR Bank Arbiter Per Client Burst Size (DDR_BURST) . . . . . . . . . . . . . . . . 97

8.1.18 DDR Bank Arbiter Per Client Burst Size 2 (DDR_BURST2) . . . . . . . . . . . . . 98

8.1.19 DDR AHB Master Timeout Control (DDR_AHB_MASTER_TIMEOUT_MAX)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...98

8.1.20 DDR AHB Timeout Current Count (DDR_AHB_MASTER_TIMEOUT_

CURNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

8.1.21 Timeout Slave Address (AHB_MASTER_TIMEOUT_SLV_ADDR) . . . . . . 99

8.1.22 DDR Controller Configuration (DDR_CTL_CONFIG) . . . . . . . . . . . . . . . . . . 99

8.1.23 DDR Self Refresh Control . . . . . . . . . . . . . . . . . . . . . . . . . (DDR_SF_CTL) 101

8.1.24 Self Refresh Timer (SF_TIMER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

8.1.25 WMAC Flush (WMAC_FLUSH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

8.1.26 DDR3 Configuration Register (DDR3_CONFIG) . . . . . . . . . . . . . . . . . . . . . 102

8.2 I2C Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

8.2.1 I2C Configuration (IC_CON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

8.2.2 I2C Target Address (IC_TAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

8.2.3 I2C HS Mode Master Code (IC_HS_MADDR) . . . . . . . . . . . . . . . . . . . . . . . 105

8.2.4 I2C Rx/Tx Data Buffer and Command (IC_DATA_CMD) . . . . . . . . . . . . . . 106

8.2.5 Standard I2C Clock SCL High Count (IC_SS_SCL_HCNT) . . . . . . . . . . . . 106

8.2.6 Standard I2C Clock SCL Low Count (IC_SS_SCL_LCNT) . . . . . . . . . . . . . 107

8.2.7 Fast I2C Clock SCL High Count (IC_FS_SCL_HCNT) . . . . . . . . . . . . . . . . 107

8.2.8 Fast I2C Clock SCL Low Count (IC_FS_SCL_LCNT) . . . . . . . . . . . . . . . . . 108

8.2.9 High Speed I2C Clock SCL High Count (IC_HS_SCL_HCNT) . . . . . . . . . . 108

8.2.10 High Speed I2C Clock SCL Low Count (IC_HS_SCL_LCNT) . . . . . . . . . . 109

8.2.11 I2C Raw Interrupt Status (IC_RAW_INTR_STAT) . . . . . . . . . . . . . . . . . . . . 109

8.2.12 I2C Interrupt Mask (IC_INTR_MASK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

8.2.13 I2C Interrupt Status (IC_INTR_STAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

8.2.14 I2C Receive FIFO Threshold (IC_RX_TL) . . . . . . . . . . . . . . . . . . . . . . . . . . 113

剩余357页未读,继续阅读

yofa2008

- 粉丝: 9

- 资源: 27

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 数据结构1800题含完整答案详解.doc

- 医疗企业薪酬系统设计与管理方案.pptx

- 界面与表面技术界面理论与表面技术要点PPT学习教案.pptx

- Java集合排序及java集合类详解(Collection、List、Map、Set)讲解.pdf

- 网页浏览器的开发 (2).pdf

- 路由器原理与设计讲稿6-交换网络.pptx

- 火电厂锅炉过热汽温控制系统设计.doc

- 企业识别CIS系统手册[收集].pdf

- 物业管理基础知识.pptx

- 第4章财务预测.pptx

- 《集成电路工艺设计及器件特性分析》——实验教学计算机仿真系.pptx

- 局域网内共享文件提示没有访问权限的问题借鉴.pdf

- 第5章网络营销策略.pptx

- 固井质量测井原理PPT教案.pptx

- 毕业实习总结6篇.doc

- UGNX建模基础篇草图模块PPT学习教案.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0