没有合适的资源?快使用搜索试试~ 我知道了~

首页PCIE SPEC 2.0

资源详情

资源评论

资源推荐

PCI Express

®

2.0

Base Specification

Revision 0.9

September 11, 2006

2

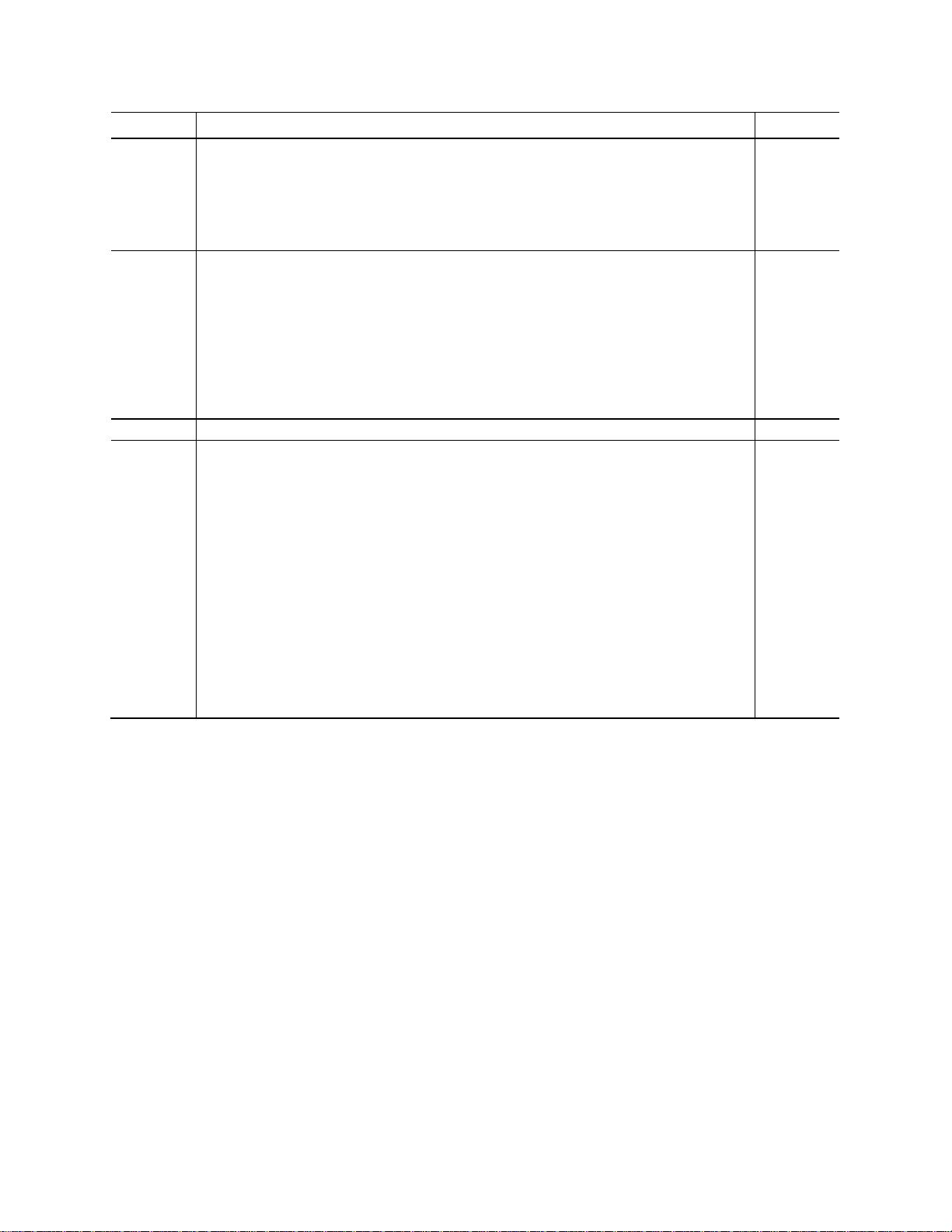

Revision Revision History DATE

0.5

PCI-SIG 0.5 draft. Incorporated the following ECNs/ECRs:

• Trusted Configuration Space for PCI Express, 23 March 2005, updated 1 July 2005

• Link Speed Management, updated 25 August 2005

• PCI Express Capability Structure Expansion, 21 March 2005, updated 19 August 2005

• Link Bandwidth Notification Mechanism, 20 April 2005, updated 26 August 2005

Also added Errata for the PCI Express Base Specification, Revision 1.1, released 1 August 2005

9/16/05

0.7

PCI-SIG 0.7 draft. Incorporated the following ECNs/ECRs:

• PCI Express Capability Structure Expansion, 21 March 2005, updated 3 November

2005

• Link Bandwidth Notification Mechanism, 20 April 2005, updated 2 November 2005

• Completion Timeout Control Capability, 27 April 2005, updated 3 November 2005

• Function Level Reset (FLR), 12 July 2005

• PCI Express Access Control Services (ACS), 27 September 2005

Also added Errata for the PCI Express Base Specification, Revision 1.1, released 31 October

2005

11/14/05

0.7a Corrected cut and paste errors in 0.7 draft dated 11/14/05 4/10/06

0.9 Incorporated the following ECNs/ECRs:

Link Bandwidth Notification Mechanism, 20 April 2005, updated 13 April 2006

Power Limit Re-definition, 2 May 2006

PCI Express Access Control Services (ACS), 27 September 2005, updated 1 June 2006

Added Errata for the PCI Express Base Specification, Revision 1.1, Second release, 8 May 2006,

updated 15 June 2006

Incorporated the following ECRs:

Function Level Reset (FLR), 12 July 2005, Updated 16 June 2006

Function Level Reset (FLR), 12 July 2005, Updated 23 June 2006

Additional edits to Link registers, etc.

Incorporated the Link Bandwidth Notification ECR, 20 April 2005, updated 28 June 2006

Updates from EWG.

Added Errata for the PCI Express Base Specification, Revision 1.1, Third release, 25 August 2006

Terminology updates from PWG.

9/11/06

PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no

responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information

contained herein.

Contact the PCI-SIG office to obtain the latest revision of this specification.

Questions regarding the PCI Express Base Specification or membership in PCI-SIG may be forwarded to:

Membership Services

www.pcisig.com

E-mail: administration@pcisig.com

Phone: 503-619-0569

Fax: 503-644-6708

Technical Support

techsupp@pcisig.com

DISCLAIMER

This PCI Express Base Specification is provided “as is” with no warranties whatsoever, including any warranty of

merchantability, noninfringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal,

specification, or sample. PCI-SIG disclaims all liability for infringement of proprietary rights, relating to use of information in this

specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

PCI Express, PCIe, and PCI-SIG are registered trademarks of PCI-SIG.

All other product names are trademarks, registered trademarks, or servicemarks of their respective owners.

Copyright © 2002-2006 PCI-SIG

PCI EXPRESS 2.0 BASE SPECIFICATION, REV. 0.9

3

Contents

OBJECTIVE OF THE SPECIFICATION.................................................................................... 21

DOCUMENT ORGANIZATION ................................................................................................ 21

DOCUMENTATION CONVENTIONS...................................................................................... 22

TERMS AND ACRONYMS........................................................................................................ 23

REFERENCE DOCUMENTS...................................................................................................... 29

1. INTRODUCTION ................................................................................................................ 31

1.1. A THIRD GENERATION I/O INTERCONNECT ................................................................... 31

1.2. PCI EXPRESS LINK......................................................................................................... 33

1.3. PCI EXPRESS FABRIC TOPOLOGY .................................................................................. 34

1.3.1. Root Complex........................................................................................................ 35

1.3.2. Endpoints .............................................................................................................. 36

1.3.3. Switch.................................................................................................................... 39

1.3.4. Root Complex Event Collector.............................................................................. 40

1.3.5. PCI Express-PCI Bridge....................................................................................... 40

1.4. PCI EXPRESS FABRIC TOPOLOGY CONFIGURATION....................................................... 40

1.5. PCI EXPRESS LAYERING OVERVIEW.............................................................................. 41

1.5.1. Transaction Layer................................................................................................. 42

1.5.2. Data Link Layer.................................................................................................... 42

1.5.3. Physical Layer ...................................................................................................... 43

1.5.4. Layer Functions and Services............................................................................... 43

2. TRANSACTION LAYER SPECIFICATION ..................................................................... 47

2.1. T

RANSACTION LAYER OVERVIEW.................................................................................. 47

2.1.1. Address Spaces, Transaction Types, and Usage................................................... 48

2.1.2. Packet Format Overview ...................................................................................... 50

2.2. TRANSACTION LAYER PROTOCOL - PACKET DEFINITION............................................... 52

2.2.1. Common Packet Header Fields ............................................................................ 52

2.2.2. TLPs with Data Payloads - Rules......................................................................... 54

2.2.3. TLP Digest Rules .................................................................................................. 56

2.2.4. Routing and Addressing Rules.............................................................................. 57

2.2.5. First/Last DW Byte Enables Rules........................................................................ 60

2.2.6. Transaction Descriptor......................................................................................... 62

2.2.7. Memory, I/O, Configuration, and Trusted Configuration Request Rules............. 67

2.2.8. Message Request Rules......................................................................................... 70

2.2.9. Completion Rules.................................................................................................. 82

2.3. H

ANDLING OF RECEIVED TLPS...................................................................................... 84

2.3.1. Request Handling Rules........................................................................................ 87

PCI EXPRESS 2.0 BASE SPECIFICATION, REV. 0.9

4

2.3.2. Completion Handling Rules................................................................................ 100

2.4. TRANSACTION ORDERING............................................................................................ 102

2.4.1. Transaction Ordering Rules ............................................................................... 102

2.4.2. Update Ordering and Granularity Observed by a Read Transaction................ 106

2.4.3. Update Ordering and Granularity Provided by a Write Transaction................ 107

2.5. VIRTUAL CHANNEL (VC) MECHANISM........................................................................ 108

2.5.1. Virtual Channel Identification (VC ID).............................................................. 110

2.5.2. TC to VC Mapping.............................................................................................. 111

2.5.3. VC and TC Rules................................................................................................. 112

2.6. ORDERING AND RECEIVE BUFFER FLOW CONTROL ..................................................... 113

2.6.1. Flow Control Rules............................................................................................. 114

2.7. DATA INTEGRITY ......................................................................................................... 124

2.7.1. ECRC Rules ........................................................................................................ 124

2.7.2. Error Forwarding............................................................................................... 129

2.8. COMPLETION TIMEOUT MECHANISM ........................................................................... 131

2.9. LINK STATUS DEPENDENCIES ...................................................................................... 132

2.9.1. Transaction Layer Behavior in DL_Down Status............................................... 132

2.9.2. Transaction Layer Behavior in DL_Up Status ................................................... 133

3. DATA LINK LAYER SPECIFICATION.......................................................................... 135

3.1. DATA LINK LAYER OVERVIEW .................................................................................... 135

3.2. DATA LINK CONTROL AND MANAGEMENT STATE MACHINE ...................................... 137

3.2.1. Data Link Control and Management State Machine Rules ................................ 138

3.3. FLOW CONTROL INITIALIZATION PROTOCOL ............................................................... 140

3.3.1. Flow Control Initialization State Machine Rules ............................................... 140

3.4. DATA LINK LAYER PACKETS (DLLPS)........................................................................ 144

3.4.1. Data Link Layer Packet Rules ............................................................................ 144

3.5. DATA INTEGRITY ......................................................................................................... 149

3.5.1. Introduction......................................................................................................... 149

3.5.2. LCRC, Sequence Number, and Retry Management (TLP Transmitter).............. 149

3.5.3. LCRC and Sequence Number (TLP Receiver).................................................... 162

4. PHYSICAL LAYER SPECIFICATION............................................................................ 171

4.1. INTRODUCTION ............................................................................................................ 171

4.2. L

OGICAL SUB-BLOCK................................................................................................... 171

4.2.1. Symbol Encoding ................................................................................................ 172

4.2.2. Framing and Application of Symbols to Lanes................................................... 175

4.2.3. Data Scrambling................................................................................................. 178

4.2.4. Link Initialization and Training.......................................................................... 180

4.2.5. Link Training and Status State Machine (LTSSM) Descriptions........................ 192

4.2.6. Link Training and Status State Rules.................................................................. 195

4.2.7. Clock Tolerance Compensation.......................................................................... 242

4.2.8. Compliance Pattern ............................................................................................ 244

4.2.9. Modified Compliance Pattern............................................................................. 245

4.3. E

LECTRICAL SUB-BLOCK ............................................................................................. 246

4.3.1. Maintaining Backwards Compatibility............................................................... 246

4.3.2. Jitter Budgeting and Measurement..................................................................... 248

PCI EXPRESS 2.0 BASE SPECIFICATION, REV. 0.9

5

4.3.3. Transmitter Specification.................................................................................... 249

4.3.4. Receiver Specification......................................................................................... 265

4.3.5. Transmitter and Receiver DC Specifications...................................................... 277

4.3.6. Channel Specifications........................................................................................ 282

4.3.7. Reference Clock Specifications........................................................................... 288

5. POWER MANAGEMENT................................................................................................. 297

5.1. OVERVIEW ................................................................................................................... 297

5.1.1. Statement of Requirements.................................................................................. 298

5.2. L

INK STATE POWER MANAGEMENT............................................................................. 298

5.3. PCI-PM

SOFTWARE COMPATIBLE MECHANISMS......................................................... 304

5.3.1. Device Power Management States (D-States) of a Function.............................. 304

5.3.2. PM Software Control of the Link Power Management State.............................. 308

5.3.3. Power Management Event Mechanisms............................................................. 313

5.4. N

ATIVE PCI EXPRESS POWER MANAGEMENT MECHANISMS....................................... 320

5.4.1. Active State Power Management (ASPM) .......................................................... 320

5.5. A

UXILIARY POWER SUPPORT....................................................................................... 338

5.5.1. Auxiliary Power Enabling................................................................................... 338

5.6. POWER MANAGEMENT SYSTEM MESSAGES AND DLLPS............................................. 339

6. SYSTEM ARCHITECTURE ............................................................................................. 341

6.1. INTERRUPT AND PME SUPPORT ................................................................................... 341

6.1.1. Rationale for PCI Express Interrupt Model........................................................ 341

6.1.2. PCI Compatible INTx Emulation........................................................................ 342

6.1.3. INTx Emulation Software Model ........................................................................ 342

6.1.4. Message Signaled Interrupt (MSI/MSI-X) Support............................................. 342

6.1.5. PME Support....................................................................................................... 344

6.1.6. Native PME Software Model .............................................................................. 344

6.1.7. Legacy PME Software Model ............................................................................. 345

6.1.8. Operating System Power Management Notification........................................... 345

6.1.9. PME Routing Between PCI Express and PCI Hierarchies ................................ 345

6.2. E

RROR SIGNALING AND LOGGING................................................................................ 346

6.2.1. Scope................................................................................................................... 346

6.2.2. Error Classification............................................................................................ 346

6.2.3. Error Signaling................................................................................................... 348

6.2.4. Error Logging..................................................................................................... 355

6.2.5. Sequence of Device Error Signaling and Logging Operations .......................... 359

6.2.6. Error Message Controls ..................................................................................... 360

6.2.7. Error Listing and Rules ...................................................................................... 361

6.2.8. Virtual PCI Bridge Error Handling.................................................................... 365

6.3. VIRTUAL CHANNEL SUPPORT ...................................................................................... 366

6.3.1. Introduction and Scope....................................................................................... 366

6.3.2. TC/VC Mapping and Example Usage................................................................. 367

6.3.3. VC Arbitration .................................................................................................... 369

6.3.4. Isochronous Support........................................................................................... 377

6.4. DEVICE SYNCHRONIZATION......................................................................................... 380

6.5. L

OCKED TRANSACTIONS.............................................................................................. 381

剩余631页未读,继续阅读

ustczeroplus

- 粉丝: 0

- 资源: 6

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 数据结构1800题含完整答案详解.doc

- 医疗企业薪酬系统设计与管理方案.pptx

- 界面与表面技术界面理论与表面技术要点PPT学习教案.pptx

- Java集合排序及java集合类详解(Collection、List、Map、Set)讲解.pdf

- 网页浏览器的开发 (2).pdf

- 路由器原理与设计讲稿6-交换网络.pptx

- 火电厂锅炉过热汽温控制系统设计.doc

- 企业识别CIS系统手册[收集].pdf

- 物业管理基础知识.pptx

- 第4章财务预测.pptx

- 《集成电路工艺设计及器件特性分析》——实验教学计算机仿真系.pptx

- 局域网内共享文件提示没有访问权限的问题借鉴.pdf

- 第5章网络营销策略.pptx

- 固井质量测井原理PPT教案.pptx

- 毕业实习总结6篇.doc

- UGNX建模基础篇草图模块PPT学习教案.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论12